# Compositional Verification of a Baby Virtual Memory Manager

Alexander Vaynberg and Zhong Shao

Yale University

Abstract. A virtual memory manager (VMM) is a part of an operating system that provides the rest of the kernel with an abstract model of memory. Although small in size, it involves complicated and interdependent invariants that make monolithic verification of the VMM and the kernel running on top of it difficult. In this paper, we make the observation that a VMM is constructed in layers: physical page allocation, page table drivers, address space API, etc., each layer providing an abstraction that the next layer utilizes. We use this layering to simplify the verification of individual modules of VMM and then to link them together by composing a series of small refinements. The compositional verification also supports function calls from less abstract layers into more abstract ones, allowing us to simplify the verification of initialization functions as well. To facilitate such compositional verification, we develop a framework that assists in creation of verification systems for each layer and refinements between the layers. Using this framework, we have produced a certification of BabyVMM, a small VMM designed for simplified hardware. The same proof also shows that a certified kernel using BabyVMM's virtual memory abstraction can be refined following a similar sequence of refinements, and can then be safely linked with BabyVMM. Both the verification framework and the entire certification of BabyVMM have been mechanized in the Coq Proof Assistant.

# 1 Introduction

Software systems are complex feats of engineering. What makes them possible is the ability to isolate and abstract modules of the system. In this paper, we consider an operating system kernel that uses virtual memory. The majority of the kernel makes an assumption that the memory is a large space with virtual addresses and a specific interface that allows the kernel to request access to any particular page in this large space. In reality, this entire model of memory is in the imagination of the programmer, supported by a relatively small but important portion of the kernel called the virtual memory manager. The job of the virtual memory manager is to handle all the complexities of the real machine architecture to provide the primitives that the rest of the kernel can use. This is exactly how the programmer would reason about this software system.

However, when we consider verification of such code, current approaches are mostly monolithic in nature. Abstraction is generally limited to abstract data types, but such abstraction can not capture changes in the semantics of computation. For example, it is impossible to use abstract data types to make virtual memory appear to work like physical memory without changing operational semantics. To create such abstraction, a change of computational model is required. In the Verisoft project[11, 18], the abstract virtual memory is defined by creating the CVM model from VAMP architecture. In AIM[7], multiple machines are used to define interrupts in the presence of a scheduler.

These transitions to more abstract models of computation tend to be quite rare, and when present tend to be complex. The previously mentioned VAMP-CVM jump in Verisoft abstracts most of kernel functionality in one step. In our opinion, it would be better to have more abstract computation models, with smaller jumps in abstraction. First, it is easier to verify code in the most abstract computational model possible. Second, smaller abstractions tend to be easier to prove and to maintain, while larger abstractions can be still achieved by composing the smaller ones. Third, more abstractions means more modularity; changes in the internals of one module will not have global effects.

However, we do not commonly see Hoare-logic verification that encourages multiple models. The likely reason is that creating abstract models and linking across them is seen as ad-hoc and tedious additional work. In this paper we show how to reduce the effort required to define models and linking, so that code verification using multiple abstractions becomes an effective approach. More precisely, our paper makes the following contributions:

- We present a framework for quickly defining multiple abstract computational models and their verification systems.

- We show how our framework can be used to define safe cross-abstraction linking.

- We show how to modularize a virtual memory manager and define abstract computational models for each layer of VMM.

- We show a complete verification of a small proof-of-concept virtual memory manager using the Coq Proof Assistant.

The rest of this paper is organized as follows. In Section 2, we give an informal overview of our work. In Section 3, we discuss the formal details of our verification and refinement framework. In Section 4, we specialize the framework for a simple C-like language. In Section 5, we certify BabyVMM, our small virtual memory manager. Section 6 discusses the Coq proof, and Section 7 presents related work and concludes.

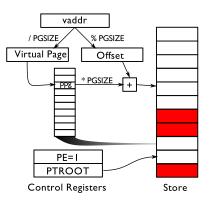

# 2 Overview and Plan for Certification

We begin the overview by explaining the design of BabyVMM, our small virtual memory manager. First, consider the model of memory present in simplified hardware (Figure 1). The memory is a storage system, which contains cells that can be read from or written to by the software. These cells are indexed by addresses. However, to facilitate indirection, the hardware includes a system called address translation (AT), which, when enabled, will cause all requests for specific addresses from the software to be translated. The AT system adds special registers to the memory system - one to enable or disable AT, and the other to point where the software-managed AT tables are located in memory. The fact that these tables are stored in memory is one of the sources of complexity in the AT system - updating AT tables requires updating in-memory tables, a process which goes through AT as well.

Fig. 1. Address Translated Hardware (HW) Model of Memory

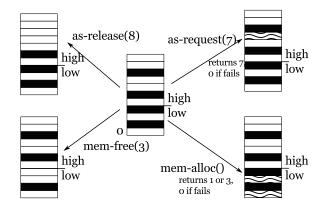

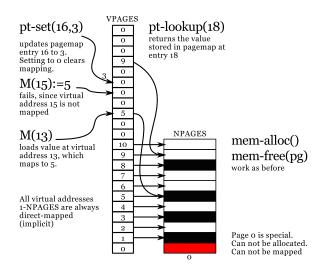

Fig. 2. Address Space (AS) Model of Memory

Because AT is such a complicated, machine-dependent, and general mechanism, BabyVMM creates an abstraction that defines specific restrictions on how AT will be used, and presents a simpler view of AT to the kernel. Although the abstract models of memory may differ depending on the features that the kernel may require, BabyVMM defines a very basic model, to which we refer as the address space (AS) model of memory (Figure 2). The AS model replaces the small physical memory with a larger virtual address space with allocatable pages and no address translation. The space is divided into high and low areas, where the low area is actually a window into physical memory (a pattern common in many kernels). Because of this distinction, the memory model has two sets of allocation functions, one for the "high" memory area where the programmer requests a specific page for allocation, and one for the "low" memory area, where the programmer can not pick which page to allocate.

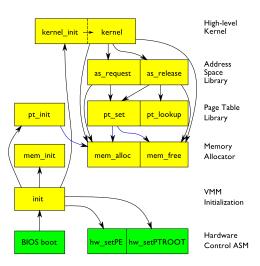

The virtual memory manager is the system that creates such an abstraction. We have implemented a small VMM, which we call BabyVMM. Its code is given in Appendix A, with the diagram of functions and function calls shown in Figure 3.

Fig. 3. Architecture of BabyVMM

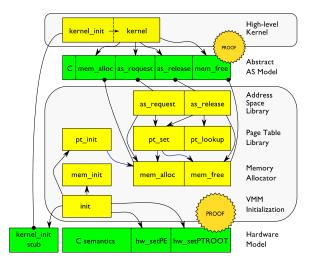

Fig. 4. Kernel Certified in the Abstraction Provided by BabyVMM

Since the address space model of memory is simpler to reason about, we would like to have the rest of the kernel certified over it, and then link the certified kernel with BabyVMM, which we will certify over the actual hardware. The plan of this certification can be seen in Figure 4. The green boxes are assumptions of the primitives, while yellow is the code. Notice how function calls (arrows) no longer go through one module to another, but instead go to the primitives that abstract the code. However, there are new connections (lines with circles) between these primitives and code, which are cross-abstraction links. These links are the tricky part, as we will have to show that the specification in one model is compatible with the implementation in another. An additional tricky part is the call of kernel\_init from init, which requires a call from

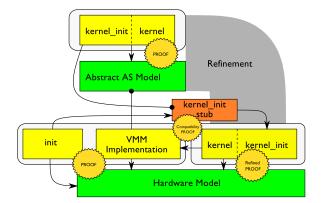

Fig. 5. Diagram of Refinement

the code in the more concrete model of memory to call a function that works over the abstract model of memory.

In practice, the way this works can be explained by the diagram in Figure 5. From the relation between the AS and Hardware models, we construct a refinement. The refinement is a set of properties over the relation between the abstract and concrete models that the programmer has to provide. Once the refinement is established, from its definition our framework creates a specification translator, that will convert any specification over the AS model into the specification over the hardware model of memory. Moreover, the refinement will guarantee that the entire kernel remains sound under the translated specification, when the calls to abstract primitives of the AS model are replaced with calls to the actual functions of VMM, which we have shown to be compatible.

This means that in the diagram, the certification of the kernel is an immediate result of the refinement, with no additional proof obligations. The proof of compatibility of the kernel and the VMM implementation is just the proofs of implementation between the functions and the primitives they implement.

The upcall of the init to the kernel\_init is handled in a similar way. Instead of proving that we can safely make the call to kernel\_init, we create a stub with a particular specification. We then show that the refined specification of the kernel\_init is compatible with the specification of the stub, which means that it is safe to replace the call to the stub with the call to the actual kernel.

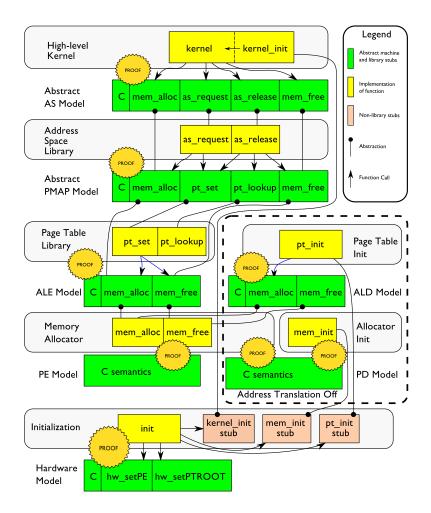

The above presented a general idea of how we certify systems with refinement in the PCC framework, where we can use two machines. Our technique however is compositional, allowing us to make smaller and simpler steps. Instead of treating entire VMM as a single abstraction, we can break it up into individual layers, such as memory allocator, hardware page table manager, and a library that provides as\_request and as\_release API to the high-level kernel. Moreover, we can simplify the certification of certain pieces by creating restricted subsets of the hardware. In the example of the kernel, the allocator initialization and the page table initialization functions all run only when the hardware does not have AT enabled, and thus we can restrict the hardware to remove AT.

Fig. 6. Complete Plan for VMM Certification

Fig. 7. Abstract State Machine

Thus, when we consider these simplifications in turn, we come up with the complete plan for certification of the kernel and the VMM implementation shown in Figure 6, which we will now put into action.  $\begin{array}{ll} id & \triangleq (\lambda \mathbb{S}. \operatorname{True}, \ \lambda \mathbb{S}. \lambda \mathbb{S}'. \mathbb{S}' = \mathbb{S}) \\ fail & \triangleq (\lambda \mathbb{S}. \operatorname{False}, \ \lambda \mathbb{S}. \lambda \mathbb{S}'. \operatorname{False}) \\ loop & \triangleq (\lambda \mathbb{S}. \operatorname{True}, \ \lambda \mathbb{S}. \lambda \mathbb{S}'. \operatorname{False}) \\ (p,g) \circ (p',g') & \triangleq (\lambda \mathbb{S}. p \ \mathbb{S} \land \forall \mathbb{S}'. g \ \mathbb{S} \ S' \to p' \ \mathbb{S}', \ \lambda \mathbb{S}. \lambda \mathbb{S}''. \exists \mathbb{S}'. g \ \mathbb{S} \ S' \land g' \ \mathbb{S}'') \\ (p,g) \oplus_{c} (p',g') & \triangleq (\lambda \mathbb{S}. (p \ \mathbb{S} \land c \ \mathbb{S}) \lor (p' \ \mathbb{S} \land \neg c \ \mathbb{S}), \lambda \mathbb{S}. \lambda \mathbb{S}'. (c \ \mathbb{S} \land g \ \mathbb{S}') \lor (\neg c \ \mathbb{S} \land g' \ \mathbb{S}')) \\ (p,g) \supseteq_{c} (p',g') & \triangleq \forall \mathbb{S}. p \ \mathbb{S} \to p' \ \mathbb{S} \land \forall \mathbb{S}, g' \ \mathbb{S}' \to g \ \mathbb{S}' \\ \end{array}$

Fig. 8. Combinators and Properties of Actions

| (Meta-program) | $\mathbb{P}$ | $::=(\mathbb{C},\mathbb{I})$                                                    | $\llbracket \mathbb{C}, \mathtt{a} \rrbracket^0_{\mathcal{M}}$                        | := loop                                                                                                                                                       |

|----------------|--------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Proc)         | $\mathbb{I}$ | $::= \texttt{nil} \mid \iota \mid \texttt{[1]} \mid \mathbb{I}_1; \mathbb{I}_2$ | $\llbracket \mathbb{C}, \mathtt{nil} \rrbracket^n_{\mathcal{M}}$                      | := id                                                                                                                                                         |

|                |              | $ (b? \mathbb{I}_1 + \mathbb{I}_2) $                                            | $\llbracket \mathbb{C}, \iota \rrbracket^n_{\mathcal{M}}$                             | $:= (\mathcal{M}(\iota))$                                                                                                                                     |

| (Proc Heap)    | $\mathbb{C}$ | $::=\{\texttt{l} \rightsquigarrow \mathbb{I}\}^*$                               | $\llbracket \mathbb{C}, [1] \rrbracket^n_{\mathcal{M}}$                               | $:= \llbracket \mathbb{C}, \mathbb{C}(1) \rrbracket_{\mathcal{M}}^{n-1}$                                                                                      |

| (Labels)       | 1            | ::= n  (nat numbers)                                                            |                                                                                       | $:= \llbracket \mathbb{C}, \rrbracket \rrbracket_{\mathcal{M}}^{n} \circ \llbracket \mathbb{C}, \rrbracket \rrbracket_{\mathcal{M}}^{n}$                      |

| (Spec Heap)    | Ψ,L          | $\mathcal{L} ::= \{1 \rightsquigarrow (p,g)\}^*$                                | $\llbracket \mathbb{C}, (b?  \mathbb{I}_1 + \mathbb{I}_2) \rrbracket^n_{\mathcal{M}}$ | $:= \llbracket \mathbb{C}, \mathbb{I}_1 \rrbracket_{\mathcal{M}}^n \bigoplus_{\mathcal{M}(b)} \llbracket \mathbb{C}, \mathbb{I}_2 \rrbracket_{\mathcal{M}}^n$ |

Fig. 9. Syntax and Semantics of the Meta-Language

# **3** Certifying with Refinement

Our framework for multi-machine certification is defined in two parts. First, we create a machine-independent verification framework that will allow us to define quickly and easily as many machines for verification as we need. Second, we will develop our notion of refinements which will allow us to link all the separate machines together.

#### 3.1 A Machine-Independent Certification Framework

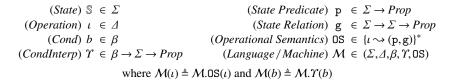

Our Hoare-logic based framework is parametric over the definition of operational semantics of the machine, and is sound no matter what machine semantics it is parameterized with. To begin defining such a framework, we first need to understand what exactly is a machine on which we can certify code. The definition that we use is given in Figure 7. Our notion of the machine consists of the following parts:

- State type ( $\Sigma$ ). Define the set of all possible states in a machine.

- Operations (△). This is a set of names of all operations that the machine supports. The set can be infinite, and defined parametrically.

- Conditionals ( $\beta$ ). Defines a type of expressions that are used for branching.

- Conditional Interpreter  $(\Upsilon)$ . Converts conditionals into state predicates.

- The operational semantics OS. This is the main portion of the machine definition. It is a set of actions (p,g) named by all operations in the machine.

The most important bit of information in the machine are the semantics (OS). The semantics of operations are defined by a precondition (p), which shows when the operation is safe to execute, and by a state relation (g) that defines the set of possible states that the operation may result in. We will refer to the pair of (p,g) as an action of the operation. Later we will also use actions to define the specification of programs.

$$\frac{\forall \mathbf{l} \in \operatorname{dom}(\mathbb{C}). \mathcal{M}, \Psi \cup \mathcal{L} \vdash \mathbb{C}(\mathbf{l}) : \Psi(\mathbf{l})}{\mathcal{M}, \mathcal{L} \vdash \mathbb{C} : \Psi} (\operatorname{code}) \qquad \frac{\mathcal{M}, \Psi \vdash \mathbb{I} : (\mathbf{p}', \mathbf{g}') \quad (\mathbf{p}, \mathbf{g}) \supseteq (\mathbf{p}', \mathbf{g}')}{\mathcal{M}, \Psi \vdash \mathbb{I} : (\mathbf{p}, \mathbf{g})} (\operatorname{weak})$$

$$\frac{\mathcal{M}, \Psi \vdash \mathbb{I}' : (\mathbf{p}', \mathbf{g}') \quad \mathcal{M}, \Psi \vdash \mathbb{I}'' : (\mathbf{p}'', \mathbf{g}'')}{\mathcal{M}, \Psi \vdash (\mathbf{b}? \ \mathbb{I}' + \mathbb{I}') : (\mathbf{p}', \mathbf{g}') \bigoplus_{\mathcal{M}(\mathbf{b})} (\mathbf{p}'', \mathbf{g}'')} (\operatorname{split}) \quad \frac{\mathcal{M}, \Psi \vdash \mathbb{I}' : (\mathbf{p}', \mathbf{g}') \quad \mathcal{M}, \Psi \vdash \mathbb{I}'' : (\mathbf{p}'', \mathbf{g}'')}{\mathcal{M}, \Psi \vdash \mathbb{I}'; \mathbb{I}'' : ((\mathbf{p}', \mathbf{g}') \circ (\mathbf{p}'', \mathbf{g}''))} (\operatorname{seq})$$

$$\frac{\mathcal{M}, \Psi \vdash (\mathbf{b}? \ \mathbb{I}' + \mathbb{I}') : (\mathbf{p}', \mathbf{g}') \bigoplus_{\mathcal{M}(\mathbf{b})} (\mathbf{p}'', \mathbf{g}'')}{\mathcal{M}, \Psi \vdash (\mathbf{l}] : \Psi(\mathbf{l})} (\operatorname{call}) \qquad \frac{\mathcal{M}, \Psi \vdash \operatorname{nil} : id}{\mathcal{M}, \Psi \vdash \operatorname{nil} : id} (\operatorname{NIL})$$

Fig. 10. Static Semantics of the Meta-Language

Because the type of actions is somewhat complex, we define action combinators in Figure 8, including composition and branching. The same figure also shows the weaker than relation between actions.

Although, at this point we have defined our machines, it does not have any notion of computation. To make use of the machine, we will need to define a concept of programs, as well as what it means for the particular program to execute.

The definition of the program is given in Figure 9. The most important definition in that figure is that of the procedure,  $\mathbb{I}$ . The procedure is a bit of program logic that sequences together calls to the operations of a machine ( $\iota$ ), or to other procedures [1] (loops are implemented as recursive calls). Procedures also include a way to branch on a condition. The procedures can be given a name, and placed in the procedure heap  $\mathbb{C}$ , where they can be referenced from other procedures through the [1] constructor. The procedure heap together with a program rest (the currently executing procedure) makes up the program that can be executed.

The meaning of executing a program is given by the indexed denotational semantics shown on the right side of Figure 9. The meaning of the program is an action that is constructed by sequencing operations. As programs can be infinite, the semantics are indexed by the depth of procedure inclusion.

We use the static semantics (Figure 10) to approximate the action of a procedure. These semantics are similar to the denotational semantics of the meta-language, except that the specifications of called procedure are looked up in the table ( $\Psi$ ). This means that the static semantics works by the programmer approximating the actions of (specifying) the program, and then making sure that the actual action of the program is within the specifications. These well-formed procedures are then grouped into a well-formed module using the CODE rule, which forms the concept of a certified module  $\mathcal{M}, \mathcal{L} \vdash \mathbb{C} : \Psi$ , where every procedure in  $\mathbb{C}$  is well-formed under specification in  $\Psi$ . The module also defines a library ( $\mathcal{L}$ ) which is a set of specifications of stubs, i.e. procedures that are used by the module, but are not in the module. These stubs can then be eliminated by providing procedures that match the stubs (see Section 3.2). For a program to be completely certified, all stubs must either be considered valid primitives or eliminated.

The soundness and correctness theorems need to show that if we checked the wellformedness of our specification, then the specifications are indeed the approximations of the actual actions. The first such theorem checks this property for the individual procedure for the maximum depth of *n* for procedure inclusion, and assumes that all the functions have been checked for depth n - 1.

#### Theorem 1 (Indexed Partial Correctness of Procedures).

If  $\mathcal{M}, \mathcal{\Psi} \vdash \mathbb{I}$ : a and  $\mathcal{M}, \emptyset \vdash \mathbb{C}$ :  $\mathcal{\Psi}$  and  $\forall f \in \mathsf{dom}(\mathbb{C})$ .  $\mathcal{\Psi}(f) \supseteq \llbracket \mathbb{C}, \mathbb{C}(f) \rrbracket_{\mathcal{M}}^{n-1}$ , then a  $\supseteq \llbracket \mathbb{C}, \mathbb{I} \rrbracket_{\mathcal{M}}^{n}$ .

### Pf.

If n = 0, then  $\llbracket \mathbb{C}, \rrbracket \rrbracket_{\mathcal{M}}^{n} = loop$ . Since for any  $a, a \supseteq loop$ , the result is trivial. If n > 0, proceed by induction on  $\mathbb{I}$ . Most cases are trivial, but rely on properties of  $\supseteq$ . The trivial, interesting case is  $\mathbb{I} = [1]$ . By definition of  $\llbracket \mathbb{C}, [1] \rrbracket_{\mathcal{M}}^{n} = \llbracket \mathbb{C}, \mathbb{C}(1) \rrbracket_{\mathcal{M}}^{n-1}$ . By our assumption  $\Psi(1) \supseteq \llbracket \mathbb{C}, \mathbb{C}(1) \rrbracket_{\mathcal{M}}^{n-1}$ , as needed.

Using this theorem, we can build up the correctness of modules to an arbitrary depth, as shown by the next theorem.

### Theorem 2 (Indexed Partial Correctness for Modules).

If  $\mathcal{M}, \emptyset \vdash \mathbb{C} : \Psi$ , then for any index *n*, for every label  $f \in \mathsf{dom}(\mathbb{C}), \Psi(f) \supseteq \llbracket \mathbb{C}, \mathbb{C}(f) \rrbracket_{\mathcal{M}}^{n}$ .

**Pf.** By induction on *n*. If n = 0, result is trivial by theorem 1. If n > 0, by IH,  $\forall 1 \in dom(\mathbb{C})$ .  $\mathscr{V}(1) \supseteq \llbracket \mathbb{C}, \mathbb{C}(1) \rrbracket_{\mathcal{M}}^{n-1}$ Apply theorem 1 to every  $\mathbb{C}(1)$ , to get the needed result.

Thus, if we show a module that is free of stubs to be well-formed, then we know that the program will obey the specifications we have given to the code.

### 3.2 Linking

When we certify using modules, it will be very common that the module will require stubs for the procedures of another module. Linking two modules together should replace the stubs in both modules for the actual procedures that are now present in the linked code. The general way to accomplish this is by the following linking lemma:

### Theorem 3 (Linking).

$$\frac{\mathcal{M}, \mathcal{L}_{1} \vdash \mathbb{C}_{1} : \Psi_{1} \quad \mathcal{M}, \mathcal{L}_{2} \vdash \mathbb{C}_{2} : \Psi_{2} \quad \mathbb{C}_{1} \perp \mathbb{C}_{2} \quad \mathcal{L}_{1} \perp \Psi_{2} \quad \mathcal{L}_{2} \perp \Psi_{1} \quad \mathcal{L}_{1} \perp \mathcal{L}_{2}}{\mathcal{M}, ((\mathcal{L}_{1} \cup \mathcal{L}_{2}) \setminus (\Psi_{1} \cup \Psi_{2})) \vdash \mathbb{C}_{1} \cup \mathbb{C}_{2} : \Psi_{1} \cup \Psi_{2}} \quad (\text{LINK})$$

where  $\Psi_{1} \perp \Psi_{2} \triangleq \forall 1 \in \text{dom}(\Psi_{1}). (1 \notin \text{dom}(\Psi_{2}) \lor \Psi_{1}(1) = \Psi_{2}(1)).$

Pf. By inversion on the two assumption, and then applying CODE rule to get the final result.

However, the above rule does not always apply immediately. When the two modules are developed independently, it is possible that the stubs of one module are weaker than the specifications of the procedures that will replace the stubs, which breaks the linking lemma. To fix this, we strengthen the library.

#### Theorem 4 (Stub Strengthening).

If  $\mathcal{M}, \mathcal{L} \vdash \mathbb{C} : \mathcal{\Psi}$ , then for any  $\mathcal{L}'$  s.t.  $\forall l \in dom(\mathcal{L})$ .  $\mathcal{L}(l) \supseteq \mathcal{L}'(l)$  and  $dom(\mathcal{L}') \cap dom(\mathcal{\Psi}) = \emptyset$ , the following holds:  $\mathcal{M}, \mathcal{L}' \vdash \mathbb{C} : \mathcal{\Psi}$ .

$$\frac{\overline{T_{a}(\mathcal{M}_{A}(\iota_{A})) \supseteq \mathcal{M}_{C}(\iota_{A})}}{\overline{T_{a}(id_{A}) \supseteq id_{C}}} \qquad \frac{(p_{A}, g_{A}) \supseteq (p'_{A}, g'_{A})}{\overline{T_{a}(p_{A}, g_{A}) \supseteq T_{a}(p'_{A}, g'_{A})}}$$

$$\frac{\overline{T_{a}((p_{A}, g_{A}) \bigoplus_{\mathcal{M}_{A}(b)} (p'_{A}, g'_{A})) \supseteq (T_{a}(p_{A}, g_{A}) \bigoplus_{\mathcal{M}_{C}(b)} T_{a}(p'_{A}, g'_{A}))}}{\overline{T_{a}((p_{A}, g_{A}) \circ (p'_{A}, g'_{A})) \supseteq (T_{a}(p_{A}, g_{A}) \circ T_{a}(p'_{A}, g'_{A}))}}$$

Fig. 11. Requirements for Relation of Actions

**Pf.** Induct over every procedure in the code heap, one by one. For every call to the stub, use the weakening rule to weaken the new stronger stub to the previous weaker specification.

This theorem allows us to strengthen the stubs to match the specs of procedures, enabling the linking lemma. Of course, if the specs of the real procedures are not stronger than the specs of the stubs, then the procedures do not correctly implement what the module expects, and linking is not possible.

### 3.3 The Refinement Framework

Up to this point, we have only considered what happens to the code that is certified over a single machine. However, the purpose of our framework is to facilitate multi-machine verification. For this purpose, we construct the refinement framework that will allow us to refine certified modules in one machine to certified modules in another. The most general notion of refinement in our framework can be defined by the following:

#### Definition 1 (Certified Refinement).

A certified refinement from machine  $\mathcal{M}_A$  to machine  $\mathcal{M}_C$  is a pair of relations  $(T_{\mathbb{C}}, T_{\Psi})$  and a predicate over the abstract certified module *Acc*, such that for all  $\mathbb{C}_A, \Psi'_A, \Psi_A$ , the following holds

$$\frac{\mathcal{M}_{A}, \mathcal{\Psi}'_{A} \vdash \mathbb{C}_{A} : \mathcal{\Psi}_{A} \quad Acc\left(\mathcal{M}_{A}, \mathcal{\Psi}'_{A} \vdash \mathbb{C}_{A} : \mathcal{\Psi}_{A}\right)}{\mathcal{M}_{C}, T_{\Psi}(\mathcal{\Psi}'_{A}) \vdash T_{\mathbb{C}}(\mathbb{C}_{A}) : T_{\Psi}(\mathcal{\Psi}_{A})} \text{ Refine}$$

This definition is not a rule, but a template for other definitions. To define a refinement, one has to provide the particular  $T_{\mathbb{C}}$ ,  $T_{\Psi}$ , *Acc* together with the proof that the rule holds. However, instead of trying to define these translations directly, we will automatically generate them from the relations between the particular pairs of machines.

**Code-preserving Refinement** In our plan for certification of BabyVMM, the syntax of the language does not change, but only the state, the semantics, and the stubs change. Thus, any pair of machines  $\mathcal{M}_A$  and  $\mathcal{M}_C$  we use for certification will have the property  $\mathcal{M}_A \ \Delta = \mathcal{M}_C \ \Delta$  and  $\mathcal{M}_A \ \beta = \mathcal{M}_C \ \beta$ . This means that when we will refine the procedures of our code, the procedures and proc heaps can stay exactly the same, and only the specifications change. Using this restriction, we can define a refinement rule using only a predicate  $T_a$  that defines such a change in the specifications.

#### **Definition 2** (Code-Preserving Refinement).

Code-preserving refinement can be defined from abstract machine  $\mathcal{M}_A$  to the concrete machine  $\mathcal{M}_C$ , when the two machines share the same set of operations ( $\Delta$ ). The refinement is defined by an action translation function  $T_a$ , which must satisfy the properties in Figure 11.

We can show that by this small definition, we can generate a complete refinement rule. To do so, we define  $T_{\mathbb{C}}(\mathbb{C}) := \mathbb{C}$  and  $T_{\Psi}(\Psi) := \{T_{a}(\Psi(1)) \mid 1 \in \text{dom}(\Psi)\}$ . Now we show that the REFINE rule holds for these transformation functions.

#### Lemma 1 (Code-Preserving Refinement Valid).

Given  $T_a$  for which the properties above are true, the following is valid:

$$\frac{\mathcal{M}_A, \mathcal{L}_A, \vdash \mathbb{C} : \Psi_A}{\mathcal{M}_C, T_{\Psi}(\mathcal{L}_A) \vdash \mathbb{C} : T_{\Psi}(\Psi_A)}$$

where  $T_{\Psi}(\Psi) := \{T_{a}(\Psi(1)) \mid 1 \in \operatorname{dom}(\Psi)\}$

**Pf.** Assume that  $\mathcal{M}_A, \Psi' \vdash \mathbb{C} : \Psi$ .

It is adequate to show that for all  $l \in dom(\Psi)$ , if  $\mathcal{M}_A, \Psi' \vdash \mathbb{C}(1) : \Psi(1)$ , then  $\mathcal{M}_C, T_{\Psi}(\Psi') \vdash \mathbb{C}(1) : T_a(\Psi(1))$ .

Proceed by induction on derivation of  $\mathcal{M}_A, \Psi' \vdash \mathbb{C}(1) : \Psi(1)$ .

Each case is handled by application of the relevant properties of  $T_a$  and an application of induction hypothesis when applicable.

The [1] case is trivial since  $T_{\Psi}(\Psi')(1) = T_{a}(\Psi'(1))$  by definition of  $T_{\Psi}$ .

Thus, by defining a single  $T_a$ , we produce a functioning refinement.

**Representation Refinement** The code preserving refinement has to be defined by creating a direct transformation of an abstract specification to the concrete one, and showing that such transformation obeys certain properties. However, such specification transformations can be automatically created from the relation between the states of the two machines ( $\mathcal{M}_A$ ,  $\mathcal{M}_C$ ), which we call repr.

repr:

$$\mathcal{M}_A.\Sigma \to \mathcal{M}_C.\Sigma \to Prop$$

Using repr, we can define our specification translation function:

$$T_{A-C}(\mathbf{p}, \mathbf{g}) \triangleq \frac{(\lambda \mathbb{S}_C . \exists \mathbb{S}_A . \mathbf{repr} \ \mathbb{S}_A \ \mathbb{S}_C \land \mathbf{p} \ \mathbb{S}_A,}{\lambda \mathbb{S}_C . \lambda \mathbb{S}'_C . \forall \mathbb{S}_A . \mathbf{repr} \ \mathbb{S}_A \ \mathbb{S}_C \to \forall \mathbb{S}'_A . \mathbf{g} \ \mathbb{S}_A \ \mathbb{S}'_A \to \mathbf{repr} \ \mathbb{S}'_A \ \mathbb{S}'_C)}$$

This operation creates an concrete action from an abstract action. Informally it works as follows. There must be at least one abstract state related to the starting concrete state for which the abstract action applies. The action starting from state  $\mathbb{S}_C$  results in set containing  $\mathbb{S}'_C$ , only if for all related abstract states for which the abstract action is valid result in sets of abstract states that contain a state related to  $\mathbb{S}'_C$ . Essentially, the resulting concrete action is an intersection of all abstract actions that do not fail.

To make this approach work, we require several properties over the machines and the repr. First, the refined semantics of abstraction operations have to be weaker than the semantics of their concrete counterparts, e.g.

$$\forall \iota_A \in \mathcal{M}_A. T_{A-C}(\mathcal{M}_A(\iota_A)) \supseteq \mathcal{M}_C(\iota_A)$$

Second, the refinement must preserve the branch choice, e.g. if the refined program chooses left branch, then abstract program had to choose the left branch in all states related by repr as well. This property is ensured by requiring the following:

$$\forall b. \forall \mathbb{S}, \mathbb{S}'. (\exists \mathbb{S}_C. \mathtt{repr}(\mathbb{S}, \mathbb{S}_C) \land \mathtt{repr}(\mathbb{S}', \mathbb{S}_C)) \to (\mathcal{M}(b) \ \mathbb{S} \leftrightarrow \mathcal{M}(b) \ \mathbb{S}')$$

We now can show that  $T_{A-C}$  is a valid specification translation that supports all the properties needed for the code preserving refinement lemma to work.

#### Lemma 2 (repr-refinement valid).

Given repr with proofs of the two properties above, the following is valid:

$$\frac{\mathcal{M}_A, \mathcal{L}_A \vdash \mathbb{C} : \Psi_A}{\mathcal{M}_C, T_{\Psi}(\mathcal{L}_A) \vdash \mathbb{C} : T_{\Psi}(\Psi_A)}$$

where  $T_{\Psi}(\Psi) := \{T_{A-C}(\Psi(1)) \mid 1 \in \operatorname{dom}(\Psi))$

**Pf.** For each property listed in Figure 11, show that  $T_{A-C}$  satisfies the property. The property that relates two machines is provided by the first condition of representation-refinement. Proving the property for the branching requires branch-preservation condition. Once these properties are proven, Lemma 1 gives us the needed result.

Thus we can produce a refinement between machines that use same program by producing a repr, making sure that the repr preserves branching correct, and then checking the compatibility of operations. Once this information is provided, we can refine our abstract certified modules to automatically generate the concrete specifications as well as automatically generate a proof that the module is well formed under these new concrete specifications.

**Other Refinements** We have proven other refinements that are not needed for the current verification, but may become important if the current work is extended.

# 4 Certifying C Code

Since BabyVMM is written in C, we define a formal specification of a tiny subset of the C language using our framework. This C machine will be parameterized by the specific semantics of the memory model, as our plan required. We will also utilize the C machine to further speed up the creation of refinements.

| (State)                                     | $\mathbb{S}$ ::= (M,S)                                                                                                                                                                                                                                                                |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | M ::= (any type over which load( $M$ ,1) and store( $M$ ,1, $w$ ) are defined)                                                                                                                                                                                                        |

|                                             | $S ::= nil   Call(list w) :: S   Data(\{v \rightarrow w\} :: S)   Ret(w) :: S$                                                                                                                                                                                                        |

|                                             | e ::= se   *(e)                                                                                                                                                                                                                                                                       |

| · 1                                         | se, $b ::= w   v   binop(bop, e_1, e_2)   unop(uop, e_1)$                                                                                                                                                                                                                             |

| 1 . ,                                       |                                                                                                                                                                                                                                                                                       |

|                                             | bop ::= +  - *  /  %  ==  < <= >   =  &&                                                                                                                                                                                                                                              |

| (Unary Operators)                           | <i>uop</i> ::= !<br>v ::= (a decidable set of names)                                                                                                                                                                                                                                  |

|                                             |                                                                                                                                                                                                                                                                                       |

|                                             | w ::= n  (integers)                                                                                                                                                                                                                                                                   |

| (Operation)                                 | $\iota  ::= v := e \mid *(e_{loc}) := e \mid fcall(list e) \mid ret(e) \mid args(list v) \mid readret(v)$                                                                                                                                                                             |

| Operation $(\iota) =$                       | Action $(\mathcal{M}(\iota)) =$                                                                                                                                                                                                                                                       |

|                                             | $(\lambda \mathbb{S}. \exists S', F, w. \mathbb{S}. S = Data(F) :: S' \land eval(\mathbf{e}, \mathbb{S}) = w,$                                                                                                                                                                        |

| v := e                                      | $\lambda \mathbb{S}, \mathbb{S}', \exists S', F, w. \mathbb{S}.S = Data(F) :: S' \land eval(\mathbf{e}, \mathbb{S}) = w \land$                                                                                                                                                        |

|                                             | $\mathbb{S}'.M = \mathbb{S}.M \land \mathbb{S}'.S = Data(F\{v \rightsquigarrow w\}) :: S')$                                                                                                                                                                                           |

|                                             | $(\lambda \mathbb{S}.\exists l, w.eval(\mathbf{e}, \mathbb{S}) = w \land eval(\mathbf{e}_{loc}, \mathbb{S}) = l \land \exists M'.M' = store(M, l, w),$                                                                                                                                |

| *(e <sub>loc</sub> ) := e                   | $\lambda \mathbb{S}, \mathbb{S}', \exists l, w. eval(\mathbf{e}, \mathbb{S}) = w \land eval(\mathbf{e}_{loc}, \mathbb{S}) = l \land$                                                                                                                                                  |

|                                             | $\mathbb{S}'.M = store(\mathbb{S}.M, l, w) \land \mathbb{S}'.S = \mathbb{S}.S)$<br>( $\lambda \mathbb{S}. \exists v_1, \dots, v_n.eval(e_1, \mathbb{S}) = v_1 \land \dots \land eval(e_n, \mathbb{S}) = v_n,$                                                                         |

| fcall([a, a])                               | $ \lambda \mathbb{S}, \mathbb{S}', \exists v_1, \dots, v_n, eval(e_1, \mathbb{S}) = v_1 \land \dots \land eval(e_n, \mathbb{S}) = v_n, \\ \lambda \mathbb{S}, \mathbb{S}', \exists v_1, \dots, v_n, eval(e_1, \mathbb{S}) = v_1 \land \dots \land eval(e_n, \mathbb{S}) = v_n \land $ |

| $\operatorname{Ican}([e_1,\ldots,e_n])$     | $\mathbb{S}'.M = \mathbb{S}.M \land \mathbb{S}'.S = Call([v_1, \dots, v_n]) :: \mathbb{S}.S)$                                                                                                                                                                                         |

|                                             | $(\lambda \mathbb{S} : \exists w_1, \dots, w_n, S' : \mathbb{S} : S = Call([w_1, \dots, w_n]) :: S',$                                                                                                                                                                                 |

| $args([v_1, \ldots, v_n])$                  | $\lambda \mathbb{S}, \mathbb{S}'. \exists w_1, \dots, w_n, \mathbb{S}'. \mathbb{S}.\mathbb{S} = Call([w_1, \dots, w_n]) :: \mathbb{S}' \land$                                                                                                                                         |

|                                             | $\mathbb{S}'.M = \mathbb{S}.M \land \mathbb{S}'.S = Data(\{\mathbb{v}_1 \rightsquigarrow w_1, \dots, \mathbb{v}_n \rightsquigarrow w_n\}) :: S')$                                                                                                                                     |

|                                             | $(\lambda \mathbb{S}. \exists S', w. \mathbb{S}.S = Ret(w) :: Data(D) :: S',$                                                                                                                                                                                                         |

| readret(v)                                  | $\lambda \mathbb{S}, \mathbb{S}', \exists S', w. \mathbb{S}.S = Ret(w) :: Data(D) :: S' \land$                                                                                                                                                                                        |

|                                             | $\mathbb{S}'.M = \mathbb{S}.M \land \mathbb{S}'.S = Data(D\{v \rightsquigarrow w\}) :: S')$                                                                                                                                                                                           |

| ret(e)                                      | $(\lambda \mathbb{S}. \exists w. eval(e, \mathbb{S}) = w, \ \lambda \mathbb{S}, \mathbb{S}'. \mathbb{S}'. M = \mathbb{S}. M \land \mathbb{S}'. S = Ret(eval(e, \mathbb{S})) :: \mathbb{S}.S)$                                                                                         |

| (w                                          | if $\mathbf{e} = w$                                                                                                                                                                                                                                                                   |

| $\mathbb{S}.S(\mathbf{v})$                  | if e = v                                                                                                                                                                                                                                                                              |

| $eval(\mathbf{e}, \mathbb{S}) ::= \{load\}$ | $(\mathbb{S} M eval(e_1, \mathbb{S}))$ if $e = (*e_1)$                                                                                                                                                                                                                                |

| h(au                                        | $f = v$ $(\mathbb{S}.M, eval(e_1, \mathbb{S}))  \text{if } e = (*e_1)$ $al(e_1, \mathbb{S}), eval(e_2, \mathbb{S}))  \text{if } e = binop(b, e_1, e_2)$ $al(e_1, \mathbb{S}))  \text{if } e = unop(u, e_1)$ $al(b, \mathbb{S}) \neq 0$                                                |

|                                             | $a(\mathbf{e}_1, \mathbf{e}_2), cvar(\mathbf{e}_2, \mathbf{e}_2) \qquad \text{if } \mathbf{e} = cvar(\mathbf{e}_2, \mathbf{e}_2)$                                                                                                                                                     |

| $\Upsilon(b) ::= \lambda \mathbb{S}. evo$   | $u(\mathbf{e}_1, \mathbf{x})) \qquad 11 \mathbf{e} = unop(u, \mathbf{e}_1)$                                                                                                                                                                                                           |

| $I(D) ::= \Lambda \mathbb{S}. eV_0$         | $u(v, \omega) \neq 0$                                                                                                                                                                                                                                                                 |

Fig. 12. Primitive C-like machine

# 4.1 The Semantics of C

To define our C machine in terms of our verification framework, we need to give it a state type, a list of operations, and the semantics of those operations expressed as actions. All of these are given in Figure 12.

The state of the C machine includes two components, the stack and the memory. The stack is an abstract C stack that consists of a list of frames, which include call, data, and return frames. In the current version, the stack is independent from memory (one can think of it existing within a statically defined part of the loaded kernel). The memory model is a parameter in the C machine, meaning that it can make use of any memory model as long as it defines load and store operations. The syntax of the C machine is different from the usual definition, in that it relies on the meta-machine for its control flow by using the meta-machines call and branch. Our definition of C adds atomic operations that perform state updates. Thus the operations include two types assignments - one to stack and one to memory, and 4 operations to manipulate stack for call and return, which push and pop the frames.

Because control flow is provided by a standard machine, the code has to be modified slightly. For example, a function call of the form r = f(x) will split into a sequence of three operations: fcall([x]); [f]; readret([r]), the first setting up a call frame, the second making the call, and the third doing the cleanup. Similarly, the body of the function  $f(x){body; return(0); }$  will become args([x]); body; ret(0), as the function must first move the arguments from the call frame into a data frame. Loops have to be desugared into recursive procedures with branches. These modifications are entirely mechanical, and hence we can claim that our machine supports desugared linearized C code.

#### 4.2 Refinement in C machines

C machines at different abstraction layers differ only in their memory models, with the stack being the same. We can use this fact to generate refinements between the C machines using only the representation relation between memory models. This relation  $(M_1 \le M_2)$  can be completely arbitrary as long as these conditions hold:

$$\forall l, v. load(M_1, l) = v \rightarrow load(M_2, l) = v \forall l, v, M'_1. \left( M'_1 = (store(M_1, l, v)) \right) \rightarrow \left( M'_1 \leq (store(M_2, l, v)) \right)$$

The above properties make sure that the load and store operations of memory behave in a similar way. We construct the repr between C machine as follows:

$$\texttt{repr} := \lambda \mathbb{S}_A, \mathbb{S}_C. \ (\mathbb{S}_A.S = \mathbb{S}_C.S) \land (\mathbb{S}_A.M \leq \mathbb{S}_C.M)$$

With repr defined, we can show that the two properties needed for repr-refinement to be valid hold in all cases. First, we show the following lemma:

#### Lemma 3 (C refinement op weakening).

$$\forall \iota \in \mathcal{M}_{M1}. T_{M1-M2}(\mathcal{M}_{M1}(\iota)) \supseteq \mathcal{M}_{M2}(\iota)$$

**Pf.** First, note that for any expression e, if eval(e) works in  $\mathcal{M}_{M1}$ , the it will result in same value in  $\mathcal{M}_{M2}$  due to property of loads in related memory.

Proceed by cases of  $\iota$ . Most cases will rely on *eval* and stack updates, and hence they are trivial. The only interesting case is  $*(e_{loc}) := e$ . The property of *eval* guarantees that both expressions will compute to same values. The use the store property to conclude that the results are related by repr.

The next lemma shows that the repr does not break branches.

#### Lemma 4 (C refinement branch ok).

$$\forall b. \forall \mathbb{S}, \mathbb{S}'. (\exists \mathbb{S}_C. \mathtt{repr}(\mathbb{S}, \mathbb{S}_C) \land \mathtt{repr}(\mathbb{S}', \mathbb{S}'_C)) \to (\mathcal{M}(b) \ \mathbb{S} \leftrightarrow \mathcal{M}(b) \ \mathbb{S}')$$

| Definition           | Value                                | Description                              |

|----------------------|--------------------------------------|------------------------------------------|

| PGSIZE               | 4096                                 | Number of bytes per page                 |

| NPAGES               | unspecified                          | Number of phys. pages in memory          |

| MEMSIZE              | NPAGES*PGSIZE                        | Total bytes of memory                    |

| VPAGES               | unspecified                          | Maximum page number of a virtual address |

| Pg(addr)             | addr/PGSIZE                          | gets page of address                     |

| Off(addr)            | addr%PGSIZE                          | offset into page of address              |

| LowPg(pg)            | $0 \le pg < \text{NPAGES}$           | valid page in low memory area            |

| HighPg(pg)           | NPAGES $\leq pg < VPAGES$            | valid page in high memory area           |

| LowAddr( <i>pg</i> ) | $LowPg(Pg(addr)) \wedge addr\%8 = 0$ | valid page in low memory area            |

| HighAddr(pg)         | $HighPg(Pg(addr)) \land addr\%8 = 0$ | valid page in high memory area           |

Fig. 13. Page Definitions

**Pf.** The *b* are expressions that can not refer to memory. Since repr guarantees that stacks are the same, that means that S and S' must have equal stack, and thus  $\mathcal{M}(b)S = \mathcal{M}(b)S'$ .

At this point we have shown that if we have two machines with memory models M1 and M2, such that  $M1 \leq M2$ , we can automatically generate the repr for the two machines. We have shown that this repr satisfies all the conditions necessary to form a repr-refinement, which means that we can use the following rule for refining code:

### Corollary 1 (C Refinement).

For any two memory models M1 and M2, s.t.  $M1 \le M2$ , the following refinement works for C machines instantiated with M1 and M2.

$$\frac{\mathcal{M}_{M1}, \mathcal{L} \vdash \mathbb{C} : \Psi}{\mathcal{M}_{M2}, T_{M1-M2}(\mathcal{L}) \vdash \mathbb{C} : T_{M1-M2}(\Psi)} M1 - M2$$

**Pf.** By lemma 3 and lemma 4 our repr defines a valid repr-refinement. Then apply Lemma 2 to get the result.

Thus we know that if we have two C-machines that have related memory models, then we have a working refinement between the two machines. Our next step is the to show the relations between all the memory models shown in our plan (in Figure 6).

# 5 Virtual Memory Manager

At this point, we have all the machinery necessary to start building our certified memory manager according to the plan. The first step is to formally define and give relations between the memory models that we will use in our certification. Then we will certify the code of the modules that make up the VMM. These modules will then be refined and linked together, resulting in the conclusion that the entire BabyVMM is certified.

#### 5.1 The Memory Models

There are several memory models that are used in the verification of this work, which we have already laid out in our plan. In this section, we will give formal definitions of these models.

| (Mem                | ory System) M                                                  | ::= (D, PE, PTROOT)                                                                                                                   |                                         |

|---------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                     | (Data) D                                                       | $::= \{addr \rightsquigarrow w \mid LowAddr(add)\}$                                                                                   | $(r)\}^{*}$                             |

| (Address Translatio | on Enabled) PE                                                 | ::= bool                                                                                                                              |                                         |

| (Pointer t          | o AT Table) PTR                                                | DOT ::= $w$ (address)                                                                                                                 |                                         |

|                     |                                                                |                                                                                                                                       |                                         |

| 1                   | Notation                                                       | Definition                                                                                                                            |                                         |

| l                   | load(M,vaddr)                                                  | $D(trans_M(vaddr))$                                                                                                                   |                                         |

| 5                   | store(M, vaddr, w)                                             | $(D\{(trans_M(vaddr)) \rightarrow w\}, \text{PE}, \text{PT}\}$                                                                        | ROOT)                                   |

|                     |                                                                | where                                                                                                                                 |                                         |

| $trans_M(va)$       | $:= \begin{cases} M(M.\text{PTROO}) \\ va \end{cases}$         | T + Pg(va) * 8) * PGSIZE + Off(va)                                                                                                    | if <i>M</i> .PE = <i>true</i> otherwise |

| Function            | Specification                                                  |                                                                                                                                       |                                         |

| hw_setPE            | $\lambda \mathbb{S}, \mathbb{S}'. \exists S'. \mathbb{S}.S =$  | $all([]) :: S' \land ValidPT(M.PTROOT),$<br>$Call([]) :: S' \land S'.S = Ret(0) :: S')/$<br>$rue \land S'.M.PTROOT = S.M.PTROOT$      | λ                                       |

| hw_setPTR00T        | $\lambda \mathbb{S}, \mathbb{S}', \exists S', nr. \mathbb{S}.$ | $= Call([nr]) :: S' \land ValidPT(nr),$<br>$S = Call([nr]) :: S' \land S'.S = Ret(0) :$<br>$S.M.PE \land S'.M.D = S.M.D \land S'.M.E$ |                                         |

Fig. 14. Address Translated Hardware (HW) Memory Model and Library ( $\mathcal{L}_{HW}$ )

First, Figure 13 gives several predicates and constants that are used in our memory definitions. The hardware in our system deals with memory in groups of addresses that we call pages. A page of memory is 4 KB in size, and thus has 512 64-bit words. This is reflected in the predicates PGSIZE as well as Pg(addr) and Off(addr) that allow for computations of pages and addresses. The definition of NPAGES and VPAGES are needed to define the precise size of physical memory and virtual space. This is important to be able to define whether a particular page number is in low or high memory areas, which is defined by predicates such as LowPg(pg).

Address Translated Memory Model Figure 14 gives a formal model of the address translated memory system. This model is a formal definition of the actual address translation implemented by our simplified hardware. This model includes the load and store operations from addresses, and thus satisfies the signature that is required of the memory models to be used with our C machine.

This definition of memory uses the state that consists of the data store (D), which represents the contents of the memory, and two control registers - a boolean register PE, which controls whether address translation is active or not, and PTROOT register, which points to the location of a single level pagetable within the memory. The data store is restricted to only valid addresses.

The fact that this model defines a single level pagetable can be seen in the load and store operations defined by this machine. Instead of directly accessing the data, addresses go through a translation function defined by *trans<sub>M</sub>*. That function shows the

Fig. 15. Informal Diagram of  $\mathcal{M}_{ALE}$

effect of having PE set or not, as well as the purpose of the PTROOT register, which is used as a starting address of a single level pagetable.

To deal with the registers contained in the memory, we rely on the primitive library  $\mathcal{L}_{HW}$ , which contains the stubs of two functions: hw-setPE and hw-setPTROOT. These functions can not be directly defined in C, as they need to update the registers. In real operating systems they are written in inline assembly, and linked with the code. As we currently do not target the assembly language, we simply define these as trusted primitives. The hw\_setPE primitive is used to switch the address translation on, and the hw\_setPTROOT to update the PTROOT register. The specifications of these primitives make them appear as functions, which means that we use them by setting up a call frame, calling the primitives, and then removing the return frame.

Our plan also features PE and PD memory models, which are restrictions of the HW memory model. PE requires that AT is always on and that the translation uses identity map for all addresses in physical memory. PD memory model requires that AT is off, and is used to simplify the memory model for initialization. These specializations of the memory models are straightforward simplifications of the HW model.

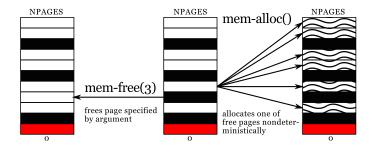

Allocated Memory Model The model that is more abstract than the hardware models is the allocated memory model named ALE when AT is enabled, and ALD when AT is disabled.

This memory model brings the notion of allocation to the memory. Before reading or writing to a memory location, the semantics will check that the address used is in the allocated page. The pages are allocated using mem\_alloc and mem\_free stubs, shown in Figure 15. The allocation of pages is non-deterministic, meaning that the programmer can not rely on getting a specific page allocated. When AT is on, it works the same way as in HW model, which means that page tables must be marked allocated, or the memory operation will fail.

The formal definition of ALE model is given in Figure 16. In addition to regular data storage (D), the model includes an allocation table, (A), which is used by the load and store operations. The operations also include predicates to make sure that the page tables are allocated and that page tables create a direct-mapped window into the physical memory as needed by our plan.

$\begin{array}{ll} (Memory \ System) & M ::= (D,A) \\ (Data \ Store) & D \ ::= \{addr \rightsquigarrow w \mid {\rm LowAddr}(addr)\}^* \\ (Page \ Allocation \ Table) & A \ ::= \{pg \rightsquigarrow {\rm bool} \mid {\rm LowPg}(pg)\}^* \end{array}$

| Notation        | Definition                                                                                                                |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------|--|

| load(M, va)     | $ \begin{array}{l} M.D(trans(M,va)) \\ \text{if } PTalloc \ M \land dm \ M \land M.A(Pg(trans(M,va)) = true \end{array} $ |  |

| store(M, va, w) | $(M.D\{trans(M,va) \rightsquigarrow w\}, M.A)$<br>if PTalloc $M \land dm M \land M.A(Pg(trans(M,va)) = true$              |  |

where

$trans(M, va) := \begin{cases} va & \text{if } \operatorname{Pg}(va) < \operatorname{NPAGES} \\ M.D(\operatorname{PTROOT} + \operatorname{Pg}(va) * 8) * \operatorname{NPAGES} + \operatorname{Off}(va) & \text{otherwise} \end{cases}$   $PTalloc(M) := \forall pg. (\operatorname{LowPage}(pg) \lor \operatorname{HighPage}(pg)) \to M.A(\operatorname{Pg}(\operatorname{PTROOT} + pg * 8)) = true$  $dm(M) := \forall vp. \operatorname{LowPg}(vp) \to \operatorname{LowAddr}(\operatorname{PTROOT} + vp * 8) \land M.D(\operatorname{PTROOT} + vp * 8) = vp$

| Function  | Specification                                                                                                                                                |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | $(\lambda \mathbb{S}. \exists S'. \mathbb{S}.S = Call([]) :: S',$                                                                                            |

| mem_alloc | $\lambda \mathbb{S}, \mathbb{S}'. \exists S'. (\mathbb{S}.S = Call([]) :: S') \land ((\mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M = \mathbb{S}.M) \lor$ |

| mem_anoc  | $(\exists pg. \mathbb{S}'.S = Ret(pg) :: S' \land \mathbb{S}'.M.A = \mathbb{S}.M.A\{pg \rightsquigarrow true\} \land$                                        |

|           | $\wedge \mathbb{S}.M.A(pg) = false \land \forall l. \mathbb{S}.M.A(Pg(l)) = true \rightarrow (\mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l))))$                     |

|           | $(\lambda \mathbb{S}. \exists S', pg. \mathbb{S}.S = Call([pg]) :: S' \land \mathbb{S}.M.A(pg) = true,$                                                      |

|           | $\lambda \mathbb{S}, \mathbb{S}', \exists S', pg. \mathbb{S}.S = Call([pg]) :: S' \land \mathbb{S}'.S = Ret(0) :: S' \land$                                  |

| mem_free  | $S'.M.A = S.M.A\{pg \rightsquigarrow false\} \land$                                                                                                          |

|           | $\forall l. S'. M. A(Pg(l)) = true \rightarrow S'. M. D(l) = S. M. D(l)$                                                                                     |

|           | )                                                                                                                                                            |

Fig. 16. Allocated Memory Model ( $M_{ALE}$ ) Semantics and Library ( $\mathcal{L}_{ALE}$ )

As the C language lacks its own primitives for modification of the allocation tables, and we want to decouple them from the memory writes, we have defined a stub library  $(\mathcal{L}_{ALE})$  that contains primitives to modify the allocation tables. The library includes two primitives: mem\_alloc for allocating a page, and mem\_free for deallocation. These stubs have fairly complex specifications. For example, the specification of mem\_alloc includes a disjunction that shows that it either returns a 0 and does not do anything or allocated some free page and returns the number of that page, all while preserving the information in all the allocated pages. These stubs mask themselves as functions, which allows us to replace these primitives with actual functions when we will link the code.

Our verification plan also includes the ALD model of memory, which is a parallel of the ALE memory model, except that AT is off, which allows some simplifications in the semantics, but the main idea behind the model does not change.

**Page Map Memory Model** The next machine in the stack of abstraction is PMAP. PMAP machine abstracts the hardware-defined pagetables into a virtual page map, hiding the actual pagetables. The machine also encodes the invariants of our page mapping,

Fig. 17. Page Map Model of Memory

| (Global Storage System) |  | ::= (D, A, PM)                                                                    |

|-------------------------|--|-----------------------------------------------------------------------------------|

| (Allocatable Memory)    |  | $::= \{addr \rightsquigarrow w \mid \text{LowPg}(Pg(addr)) \land addr\%8 = 0\}^*$ |

| (Page Allocation Table) |  | $::= \{pg \rightsquigarrow \texttt{bool} \mid \texttt{LowPg}(pg)\}^*$             |

| (Page Map)              |  | $I ::= \{pg \rightsquigarrow pg' \mid HighPg(pg)\}^*$                             |

| Notation Definition     |  |                                                                                   |

| Notation        | Definition                                            |                                   |

|-----------------|-------------------------------------------------------|-----------------------------------|

| load(M, va)     | M.D(trans(M, va))                                     | if $M.A(Pg(trans(M, va))) = true$ |

| store(M, va, w) | $(M.D\{trans(M, va) \rightsquigarrow w\}, M.A, M.PM)$ | if $M.A(Pg(trans(M, va))) = true$ |

٦

| trans(M va) := | (M.PM(Pg(va)) * PGSIZE + Off(va))<br>va | if HighPg( $Pg(va)$ ) |

|----------------|-----------------------------------------|-----------------------|

| trans(m,va) .= | (va                                     | otherwise             |

| Label      | Specification                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | $(\lambda \mathbb{S}. \exists S'. \mathbb{S}. S = Call([]) :: S',$                                                                                                              |

| mem_alloc  | $\lambda \mathbb{S}, \mathbb{S}'. \exists S'. (\mathbb{S}.S = Call([]) :: S') \land ((\mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M = \mathbb{S}.M) \lor$                    |

| Incin_anoc | $(\exists pg. S'.S = Ret(pg) :: S' \land S'.M.A = S.M.A \{ pg \rightsquigarrow true \} \land S'.M.PM = S.M.PM \land$                                                            |

|            | $\wedge \mathbb{S}.M.A(pg) = false \land \forall l. \mathbb{S}.M.A(Pg(l)) = true \rightarrow (\mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l))))$                                        |

|            | $(\lambda \mathbb{S}. \exists S', pg. \mathbb{S}.S = Call([pg]) :: S' \land \mathbb{S}.M.A(pg) = true,$                                                                         |

| mem_free   | $\lambda \mathbb{S}, \mathbb{S}', \exists S', pg. \mathbb{S}.S = Call([pg]) :: S' \land \mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M.PM = \mathbb{S}.M.PM \land$            |

|            | $\mathbb{S}'.M.A = \mathbb{S}.M.A\{pg \rightsquigarrow false\} \land \forall l. \mathbb{S}'.M.A(Pg(l)) = true \rightarrow \mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l)\}$             |

|            | $(\lambda \mathbb{S}.\exists S', vp, pp. \mathbb{S}.S = Call([vp, pp]) :: S' \land HighPg(vp) \land LowPg(pp)$                                                                  |

| pt_set     | $\lambda \mathbb{S}, \mathbb{S}', \exists S', vp, pp. \mathbb{S}.S = Call([vp, pp]) :: S' \land \mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M.A = \mathbb{S}.M.A \land \Box$ |

|            | $ \mathbb{S}'.M.PM = \mathbb{S}.M.PM\{vp \rightsquigarrow pp\} \land \forall l. \mathbb{S}'.M.A(Pg(l)) = true \rightarrow \mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l)) $             |

| pt_lookup  | $(\lambda \mathbb{S}. \exists S', vp. \mathbb{S}.S = Call([vp]) :: S' \land HighPg(vp),$                                                                                        |

|            | $\lambda \mathbb{S}, \mathbb{S}', \exists S', vp. \mathbb{S}.S = Call([vp]) :: S' \land \mathbb{S}'.S = Ret(\mathbb{S}.M.PM(vp)) :: S' \land \mathbb{S}'.M = \mathbb{S}.M)$     |

**Fig. 18.** PMAP Memory Model ( $M_{PMAP}$ ) and Library ( $\mathcal{L}_{PMAP}$ )

and also protects the page mappings from modifications by regular load and stores, making the translation system simpler. The intuitive view of this model of memory is given in Figure 17.

The formal definition of the PMAP memory model is given in Figure 18. The formal definition is fairly similar to the one in the ALE model of memory. To facilitate abstract translation, we have added an additional table PM, which contains mappings of high pages to low pages, which exists outside the main memory store. The translation function *trans* is modified to use the PM for translating high addresses, no longer looking up addresses in memory. The translation function automatically uses identity for low addresses thereby removing the need to check that the addresses inserted into the page tables are correct. Such formal definition makes PMAP appear as a concise machine-independent definition of the address translation.

We still need the stub library  $(\mathcal{L}_{PMAP})$  to perform the tasks that can not be directly controlled with the load and store operations accessible directly through C code. The library retains the stubs for the allocation tables, whose specification is similar to those in the previous library, except there is an additional condition that shows that the memory preserves the page map as well. The stub library also defines two new stubs, pt\_set and pt\_lookup, for controlling the entries in the page map. Since the translation system is completely abstract, these two stubs are the only ways to set the virtual addresses in this model.

Address Space Memory Model The most abstract memory model in our plan is  $M_{AS}$ , which will be used for the certification of the high-level kernel. We have already presented the informal view of this memory model in Section 2.

The formal definition is in Figure 19. This memory model is different from the other memory models presented in the paper. The first major change is that the data store now includes the entire virtual space. This means that in this model, storing information in virtual addresses actually uses those addresses in the store, which also means that there is no more address translation, but a large address space.

This address space still has an allocation system that the programs must follow, e.g. can not access an address that is not allocated. But other than the allocation table and the actual data store, no additional state is defined by this model.

Because of the allocation system, the AS memory model needs stubs to control the allocation tables, which are defined by the  $(\mathcal{L}_{AS})$ . However, the semantics of the low memory space (which is a window into physical memory) and the high memory space are different, and thus we define two pairs of allocation predicates. The low memory area is controlled by the already familiar mem\_alloc and mem\_free, whose semantics are similar to those of the ALE model, with only an additional precondition that makes sure that the address is in the low space. To allocate and free pages in the high memory area, the library provides as\_request and as\_release stubs. The major difference in their specifications are that as\_request takes a parameter that specifies the page number of the page that the programmer wants to allocate. Such semantics is needed in the high memory area, as the kernel may want to use specific addresses for its purposes.

(Memory System) M ::= (D, A)

(*Data Store*)  $D ::= \{addr \rightsquigarrow w \mid \text{HighAddr}(addr) \lor \text{LowAddr}(addr)\}^*$

(*Page Allocation*)  $A ::= \{pg \rightarrow bool | HighPg(pg) \lor LowPg(pg)\}^*$

| Notation        | Definition                            |                           |

|-----------------|---------------------------------------|---------------------------|

| load(M, va)     | M.D(addr)                             | if $M.A(Pg(addr)) = true$ |

| store(M, va, w) | $(M.D{addr \rightsquigarrow w}, M.A)$ | if M.A(Pg(addr)) = true   |

| Label      | Specification                                                                                                                                                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | $(\lambda \mathbb{S}. \exists S'. \mathbb{S}.S = Call([]) :: S',$                                                                                            |

| mem_alloc  | $\lambda \mathbb{S}, \mathbb{S}'. \exists S'. (\mathbb{S}.S = Call([]) :: S') \land ((\mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M = \mathbb{S}.M) \lor$ |

| mem_anoc   | $(\exists pg. \text{LowPg}(pg) \land \mathbb{S}'.S = Ret(pg) :: S' \land \mathbb{S}'.M.A = \mathbb{S}.M.A\{pg \rightsquigarrow true\} \land$                 |

|            | $\land \mathbb{S}.M.A(pg) = false \land \forall l. \mathbb{S}.M.A(Pg(l)) = true \rightarrow (\mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l))))$                      |

|            | $(\lambda \mathbb{S}. \exists S', pg. \mathbb{S}.S = Call([pg]) :: S' \land \text{LowPg}(pg) \land \mathbb{S}.M.A(pg) = true,$                               |

| mem_free   | $\lambda \mathbb{S}, \mathbb{S}', \exists S', pg.  \mathbb{S}.S = Call([pg]) :: S' \land \mathbb{S}'.S = Ret(0) :: S' \land$                                 |

| Incin_iice | $S'.M.A = S.M.A\{pg \rightsquigarrow false\} \land$                                                                                                          |

|            | $\forall l.  \mathbb{S}'.M.A(Pg(l)) = true \to \mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l))$                                                                      |

|            | $(\lambda \mathbb{S}. \exists S', vpg. \mathbb{S}.S = Call([vpg]) :: S' \land \text{HighPg}(vpg),$                                                           |

|            | $\lambda \mathbb{S}, \mathbb{S}', \exists S', vpg. \mathbb{S}.S = Call([vpg]) :: S' \land$                                                                   |

|            | $((\mathbb{S}'.S = Ret(0) :: S' \land \mathbb{S}'.M = \mathbb{S}.M) \lor$                                                                                    |

| as-request | $(\mathbb{S}'.S = Ret(vpg) :: S' \land \mathbb{S}.M.A(vpg) = false \land \mathbb{S}'.M.A = \mathbb{S}.M.A\{vpg \rightsquigarrow true\} \land$                |

|            | $\forall l.  \mathbb{S}.M.A(Pg(l)) = true \rightarrow (\mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l)))$                                                             |

|            | )                                                                                                                                                            |

|            |                                                                                                                                                              |

|            | $(\lambda \mathbb{S}. \exists S', vpg. \mathbb{S}. S = Call([vpg]) :: S' \land \mathbb{S}. M.A(pg) = true \land \text{HighPg}(vpg),$                         |

| as-release | $\lambda \mathbb{S}, \mathbb{S}', \exists S', vpg. \mathbb{S}.S = Call([vpg]) :: S' \land \mathbb{S}'.S = Ret(0) :: S' \land$                                |

| as-refease | $S'.M.A = S.M.A \{vpg \rightsquigarrow false\} \land$                                                                                                        |

|            | $\forall l.  \mathbb{S}'.M.A(Pg(l)) = true \to \mathbb{S}'.M.D(l) = \mathbb{S}.M.D(l))$                                                                      |

**Fig. 19.** Address Space ( $M_{AS}$ ) Memory Model and Library ( $\mathcal{L}_{AS}$ )

#### 5.2 Relation between Memory Models

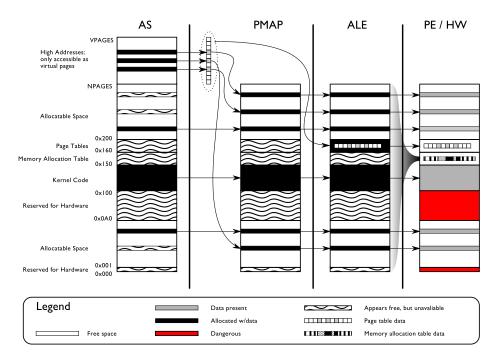

Our plan calls for creation of the refinements between the memory models. In Section 4.2, we have shown that we can generate a valid refinement by creating a relation between the memory states, and then showing that abstract loads and stores are preserved by this relation. These relations and proofs of preserving the memory operations are fairly lengthy and quite technical, and thus we leave the mathematical detail to our Coq implementation, opting for a visual description shown in Figure 20.

On the right is a state of the hardware memory, whose operational semantics gives little protection from accessing data. Some areas of memory are dangerous, some are empty, others contain data, including the allocation tables and page tables. This memory relates to the ALE memory model by abstracting out the memory allocation table. This allocation table now offers protection for accessing both the unallocated space, and the space that seems unallocated, but dangerous to use (marked by wavy lines). An example of such area is the allocation table itself - the ALE model hides the table, making it

Fig. 20. Relation between Memory Models

appear to be unusable. The ALE mem\_alloc primitive will never allocate pages from these wavy areas, protecting them without complicating the memory model.