# Modular Verification of Concurrent Assembly Code with Dynamic Thread Creation and Termination

Xinyu Feng and Zhong Shao

Department of Computer Science, Yale University New Haven, CT 06520-8285, U.S.A. {feng, shao}@cs.yale.edu

# Abstract

Proof-carrying code (PCC) is a general framework that can, in principle, verify safety properties of arbitrary machine-language programs. Existing PCC systems and typed assembly languages, however, can only handle sequential programs. This severely limits their applicability since many real-world systems use some form of concurrency in their core software. Recently Yu and Shao proposed a logic-based "type" system for verifying concurrent assembly programs. Their thread model, however, is rather restrictive in that no threads can be created or terminated dynamically and no sharing of code is allowed between threads. In this paper, we present a new formal framework for verifying general multi-threaded assembly code with unbounded dynamic thread creation and termination as well as sharing of code between threads. We adapt and generalize the rely-guarantee methodology to the assembly level and show how to specify the semantics of thread "fork" with argument passing. In particular, we allow threads to have different assumptions and guarantees at different stages of their lifetime so they can coexist with the dynamically changing thread environment. Our work provides a foundation for certifying realistic multi-threaded programs and makes an important advance toward generating proofcarrying concurrent code.

*Categories and Subject Descriptors* F.3.1 [*Logics and Meanings of Programs*]: Specifying and Verifying and Reasoning about Programs; D.2.4 [*Software Engineering*]: Software/Program Verification — correctness proofs, formal methods; D.3.1 [*Programming Languages*]: Formal Definitions and Theory—semantics; D.4.5 [*Operating Systems*]: Reliability—verification

General Terms Languages, Verification

*Keywords* Concurrency Verification, Proof-Carrying Code, Rely-Guarantee, Dynamic Thread Creation

# 1. Introduction

Proof-carrying code (PCC) [28] is a general framework that can, in principle, verify safety properties of arbitrary machine-language programs. Existing PCC systems [29, 6, 2] and typed assembly languages (TAL) [27, 26], however, can only handle *sequential* programs. This severely limits their applicability since most real-world

ICFP'05 September 26–28, 2005, Tallinn, Estonia.

Copyright © 2005 ACM 1-59593-064-7/05/0009...\$5.00.

systems use some form of concurrency in their core software. Certifying low-level concurrent programs is an important task because it helps increase the reliability of software infrastructure and is crucial for scaling the PCC and TAL technologies to realistic systems.

As an important first step, Yu and Shao [42]—at last year's ICFP—proposed a certified formal framework (known as CCAP) for specifying and reasoning about general properties of concurrent programs at the assembly level. They applied the "invariance proof" technique for verifying general safety properties and the rely-guarantee methodology [23] for decomposition. They introduced a notion of "local guarantee" for supporting thread-modular verification even inside the middle of an atomic instruction sequence. Their thread model, however, is rather restrictive in that no threads can be created or terminated dynamically and no sharing of code is allowed between threads; both of these features are widely supported and used in mainstream programming languages such as C, Java, and Concurrent ML [34].

Certifying dynamic thread creation and termination turns out to be a much harder problem than we had originally anticipated [42]. Dynamic thread creation and termination imply a changing thread *environment* (*i.e.*, the collection of all live threads in the system other than the thread under concern). Such dynamic environment cannot be tracked during static verification, yet we still must somehow reason about it. For example, we must ensure that a newly created thread does not interfere with existing live threads, but at the same time we do not want to enforce non-interference for threads that have no overlap in their lifetime. Using one copy of code to create multiple threads also complicates program specification.

Existing work on the verification of concurrent programs almost exclusively uses high-level calculi (e.g., CSP [21], CCS [25], TLA [24]). Also, existing work on the rely-guarantee methodology for shared-memory concurrency only supports properly nested concurrent code in the form of cobegin  $P_1 \parallel \ldots \parallel P_n$  coend (which is a language construct for parallel composition where code blocks  $P_1$ ,  $\ldots$ ,  $P_n$  execute in parallel and all terminate at the coend point). They do not support dynamic thread creation and termination.

Modularity is also needed to make verification scale. Existing work on the rely-guarantee methodology supports thread modularity, *i.e.*, different threads can be verified separately without looking into other threads' code. However, they do not support code reuse very well. In CCAP, if a procedure is called in more than one thread, it must be verified multiple times using different specifications, one for each calling thread. We want a procedure to be specified and verified once so it can be reused for different threads.

In this paper, we propose a new framework for supporting <u>certified multi-threaded assembly programming (CMAP)</u>. CMAP is based on a realistic abstract machine which supports dynamic thread creation with argument passing (the "fork" operation) as well as termination (the "exit" operation). Thread "join" can also be

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee.

implemented in our language using synchronization. Our approach builds on previous work on type systems and program verification but makes the following important new contributions:

- The "fork/join" thread model is more general than "cobegin/coend" in that it supports unbounded dynamic thread creation, which poses new challenges for verification. To our knowledge, our work is the first to successfully apply the relyguarantee method to verify concurrent programs with dynamic thread creation and termination. Our CMAP framework provides a foundation for certifying realistic multi-threaded programs and makes an important step toward generating concurrent certified code.

- The presence of dynamic threads makes it impossible to track the actual live threads during verification. This poses great challenge in enforcing the rely-guarantee condition. To solve this, we collect all dynamic threads into a single *environment* (*i.e.*, the dynamic thread queue) and reason about the environment's assumption and guarantee requirements as a whole. Although the dynamic thread queue cannot be tracked statically, we can update and approximate the environment's assumption and guarantee at each program point. In fact, we can unify the concepts of the current running thread's assumption/guarantee with its environment's guarantee/assumption. As we will demonstrate in Sections 3 and 4, making this work in a formal framework (*i.e.*, CMAP) is not trivial and it constitutes our main technical contribution.

- To ensure that the dynamic thread environment is well-formed, we enforce the invariant that the active threads in the system never interfere with each other. We maintain this invariant by following the approach used for type checking the dynamic data heap [27]. By combining the type-based proof techniques with the rely-guarantee based reasoning, we get a simple, extensible, and expressive framework for reasoning about the flexible "fork/join" thread model.

- We allow one copy of thread code to be activated multiple times at different places. Different "incarnations" may have different behavior, depending on the value of the thread argument. This allows us to support unbounded thread creation.

- We show how to maintain thread-modular reasoning even in the presence of dynamic thread creation and termination. Unlike CCAP, we allow each code segment to be specified independently of threads. Our work provides great support for code-and verification sharing between threads.

- We have also solved some practical issues such as thread argument passing and the saving and restoring of thread-private data at context switches. These issues are important for realistic multi-threaded programming but as far as we know have never been discussed in existing work.

We have developed CMAP and proved its soundness using the Coq proof assistant [37]. The implementation in Coq is available for download [10]. Our work makes an important advance toward building a complete PCC system for multi-threaded programs. Without formal systems such as CMAP, we cannot formally reason about concurrent assembly code. Still, more work must be done before we can construct a fully practical system. For example, a highly desirable goal is a high-level language with concise human-readable annotations that can be automatically compiled into CMAP programs and proofs. We leave this as future work.

In the rest of this paper, we first give an overview of the relyguarantee-based reasoning and a detailed explanation of the key challenges in verifying multi-threaded assembly code (Section 2). We then give an informal description of our approach to address these problems in Section 3, and present our work on CMAP with

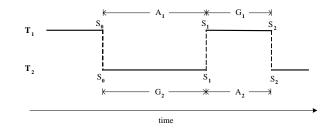

Figure 1. Rely-guarantee-based reasoning

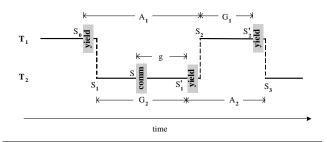

Figure 2. R-G in a non-preemptive setting

formal semantics in Section 4. We use a few examples to illustrate CMAP-based program verification in Section 5. Finally we discuss related work and conclude.

# 2. Background and Challenges

#### 2.1 Rely-Guarantee-Based Reasoning

The rely-guarantee (R-G) proof method [23] is one of the beststudied approaches to the compositional verification of sharedmemory concurrent programs. Under the R-G paradigm, every thread is associated with a pair (A, G), with the meaning that if the environment (*i.e.*, the collection of all of the rest threads) satisfies the assumption A, the thread will meet its guarantee G to the environment. In the shared-memory model, the assumption A of a thread describes what atomic transitions may be performed by other threads, while the guarantee G of a thread must hold on every atomic transition of the thread. They are typically modeled as predicates on a pair of states, which are often called *actions*.

For instance, in Figure 1 we have two interleaving threads  $T_1$  and  $T_2$ .  $T_1$ 's assumption  $A_1$  adds constraints on the transition  $(S_0, S_1)$  made by the environment  $(T_2$  in this case), while  $G_1$  describes the transition  $(S_1, S_2)$ , assuming the environment's transition satisfies  $A_1$ . Similarly  $A_2$  describes  $(S_1, S_2)$  and  $G_2$  describes  $(S_0, S_1)$ .

We need two steps to reason about a concurrent program consisting of  $T_1$  and  $T_2$ . First, we check that there is no interference between threads, i.e., that each thread's assumption can be satisfied by its environment. In our example, non-interference is satisfied as long as  $G_1 \Rightarrow A_2$  (a shorthand for  $\forall S, S'.G_1(S, S') \Rightarrow$  $A_2(S, S')$ ), and  $G_2 \Rightarrow A_1$ . Second, we check that  $T_1$  and  $T_2$  do not lie, that is, they satisfy their guarantee as long as their assumption is satisfied. As we can see, the first step only uses the specification of each thread, while the second step can be carried out independently without looking at other threads' code. This is how the R-G paradigm achieves thread-modularity.

# 2.2 R-G in Non-Preemptive Thread Model

CMAP adopts a non-preemptive thread model, in which threads yield control voluntarily with a yield instruction, as shown in Figure 2. The preemptive model can be regarded as a special case of

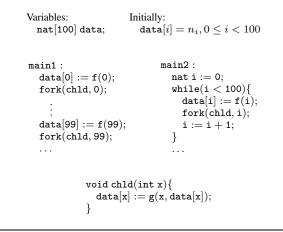

Figure 3. Loop: high-level program

the non-preemptive one, in which an explicit yield is used at every program point. Also, on real machines, programs might run in both preemptive and non-preemptive settings: preemption is usually implemented using interrupts; a program can disable the interrupt to get into non-preemptive setting.

An "atomic" transition in a non-preemptive setting then corresponds to a sequence of instructions between two yields. For instance, in Figure 2 the state pair  $(S_2, S'_2)$  corresponds to an atomic transition of thread  $T_1$ . A difficulty in modeling concurrency in such a setting is that the effect of an "atomic" transition cannot be completely captured until the end. For example, in Figure 2, the transition  $(S_1, S'_1)$  should satisfy  $G_2$ . But when we reach the intermediate state S, we have no idea of what the whole transition (*i.e.*,  $(S_1, S_1')$ ) will be. At this point, neither  $(S_1, S)$  nor  $(S, S_1')$  need satisfy  $G_2$ . Instead, it may rely on the remaining commands (the commands between comm and yield, including comm) to complete an adequate state transition. In CCAP [42], a "local guarantee" g is introduced for every program point to capture further state changes that must be made by the following commands before it is safe for the current thread to yield control. For instance, the local guarantee g attached to comm in Figure 2 describes the transition  $(S, S'_1).$

#### 2.3 Challenges for Dynamic Thread Creation

To prove safety properties of multi-threaded programs, the key problem is to enforce the invariant that *all executing threads must not interfere with each other*. As mentioned in Section 2.1, threads *do not interfere* (or they satisfy the *non-interference* or *interference-free* property) only if each thread's assumption is implied by the guarantee of all other threads<sup>1</sup>. For languages that do not support dynamic thread creation, the code for each thread corresponds to exactly one executing thread. Using the rely-guarantee method, we can assign an assumption and guarantee to each thread code and enforce non-interference by checking all of these assumptions and guarantees, as is done in [42] and [13]. However, the following example shows that this simple approach cannot support dynamic thread creation and and multiple "incarnation" of the thread code.

In Figure 3, the high-level pseudo code (using C-like syntax) shows the code for (two versions of) a main thread and child threads. The main thread initializes 100 pieces of data using some function f, and distributes them to 100 child threads that will work on their own data (by applying a function g) in parallel. The fork function creates a child thread that will execute the function pointed

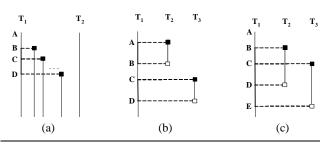

Figure 4. Interleaving of threads

to by the first argument. The second argument of fork is passed to the function as argument. The thread main1 does this in sequential code while main2 uses code with a loop. We assume that the high level code runs in preemptive mode. In other words, there is an implicit yield at any program point.

It is easy to see that both versions are "well-behaved" as long as the function g has no side effects, and all other threads in the rest of the system do not update the array of data. However, the simple approach used in [42] and [13] even cannot provide a specification for such trivial code.

1. Figure 4 (a) illustrates the execution of main1 (time goes downwards). When doing data initialization (at stage A-B, meaning from point A to point B), the main thread needs to assume that no other threads in the environment (say,  $T_2$ ) can change the array of data. However, the composition of the main thread's environment changes after a child thread is created. The assumption used at A-B is no longer appropriate for this new environment since the first child thread will write to data[0]. And the environment will keep changing with the execution of the main thread. How can we specify the main1 thread to support such a dynamic thread environment?

One possible approach is that the main thread relaxes its assumption to make exceptions for its child threads. However, it is hard to specify the parent-child relationship. Another approach is to use something like the program counter in the assumption and guarantee to indicate the phase of computation. This means the specification of the main thread is sensitive to the implementation. Also the program structure of the main thread has to be exposed to the specification of the child threads, which compromises modularity. The worst thing is that this approach simply won't work for the version main2.

- 2. Since multiple child threads are created, we must make sure that there is no interference between these children. It is easy for the above example since we can let the assumption and guarantee of the chld code be parameterized by its argument, and require  $G_i \Rightarrow A_j$  given  $i \neq j$ . However, this approach cannot be generalized for threads that have dummy arguments and their behavior does not depend on their arguments at all. In this case  $G_i \equiv G_j$  and  $A_i \equiv A_j$  for any i and j. Then requiring  $G_i \Rightarrow A_j$  is equivalent to requiring  $G_i \Rightarrow A_i$ , which cannot be true in general, given the meaning of assumptions and guarantees described in section 2.1. Do we need to distinguish these two kinds of threads and treat them differently? And how do we distinguish them?

- 3. Another issue introduced by dynamic thread creation, but not shown in this example program, is that the lifetimes of some threads may not overlap. In the case shown in Figure 4 (b), the lifetimes of  $T_2$  and  $T_3$  do not overlap and we should not statically enforce non-interference between them. Again, how can we specify and check the interleaving of threads, which can be as complex as shown in Figure 4 (c)?

<sup>&</sup>lt;sup>1</sup> We will formalize the Non-Interference property in Section 4.4.

In the next section we'll show how these issues are resolved in our development of CMAP.

# 3. Our Approach

In the rest of this paper, to distinguish the executing thread and the thread code, we call the dynamically running thread the "dynamic thread" and the thread code the "static thread". In Figure 3 the function chld is the static child thread, from which 100 dynamic child threads are activated.

As explained in Section 2.3, the approach that requiring noninterference of static threads is too rigid to support dynamic thread creation. Our approach, instead, enforces the thread noninterference in a "lazy" way. We maintain a dynamic thread queue which contains all of the active threads in the system. When a new thread is created, it is added to the dynamic thread queue. A thread is removed from the queue when its execution terminates. We also require that, when specifying the program, each static thread be assigned an assumption/guarantee pair. However, we do not check for non-interference between static thread specifications. Instead, each dynamic thread is also assigned an assumption and guarantee at the time of creation, which is an instantiation of the corresponding static thread specification with the thread argument. We require that dynamic threads do not interfere with each other, which can be checked by inspecting their specifications.

Our approach is very flexible in that each dynamic thread does not have to stick to one specification during its lifetime. When its environment changes, its specification can be changed accordingly. As long as the new specification does not introduce interference with other existing dynamic threads, and the subsequent behavior of this thread satisfies the new specification, the whole system is still interference-free. In this way, we can deal with the changing environment resulting from dynamic thread creation and termination. Problem 1 in Section 2.3 can be solved now.

If the lifetimes of two threads do not overlap they will not show up in the system at the same time. Therefore we do not need to check for interference at all. Also, since each dynamic thread has its own specification, we no longer care about the specification of the corresponding static thread. Therefor problems 2 and 3 shown in Section 2.3 are no longer an issue in our approach.

## 3.1 Typing The Dynamic Thread Queue

We define the dynamic thread queue  $\mathbb{Q}$  as a set of thread identifiers  $t_i$ , and the assignment  $\Theta$  of assumption/guarantee pairs to dynamic threads as a partial mapping from  $t_i$  to  $(A_i, G_i)^2$ . The queue  $\mathbb{Q}$  is "well-typed" with regard to  $\Theta$  if:

- $\mathbb{Q} = dom(\Theta)$ , where  $dom(\Theta)$  is the domain of  $\Theta$ ;

- threads in  $\mathbb{Q}$  do not interfere, *i.e.*,  $\forall t_i, t_j.t_i \neq t_j \Rightarrow (G_i \Rightarrow A_j)$ ; and

- each dynamic thread t<sub>i</sub> is "well-behaved" with regard to  $(A_i, G_i)$ , *i.e.*, if  $A_i$  is satisfied by the environment, t<sub>i</sub>'s execution does not get stuck and satisfies  $G_i$ .

Therefore, the invariant we need to maintain is that during the execution of the program, for the queue  $\mathbb{Q}$  at each step there exists a  $\Theta$  such that  $\mathbb{Q}$  is well-typed with regard to  $\Theta$ . In fact, we do not require  $\Theta$  to be part of the program specification. We only need to ensure that there *exists* such a  $\Theta$  at each step, which may be changing.

The content of the thread queue keeps changing, so how can we track the set of threads in the queue by a static inspection of the program? Here we follow the approach used for type-checking the

dynamic data heap [27], which is dynamically updated by the store instruction and extended by the alloc instruction. We can ensure our invariant holds as long as the following conditions are satisfied:

- At the initial state (when the program starts to run) we can find a Θ to type-check the initial Q. Usually the initial Q only contains the main thread, which will start to execute its first instruction, so we can simply assign the assumption/guarantee in the specification of the static main thread to the dynamic main thread.

- For each instruction in the program, assume that before the execution of the instruction there is a Θ such that Q is well typed. Then as long as certain constraints are satisfied to execute the instruction, there must exist a Θ' that can type check the resulting Q'. For most instructions which do not change the content of the thread queue, this condition can be trivially satisfied. We are only interested in the "fork" and "exit" operation which will change the content of Q.

For the "exit" instruction, the second condition can also be satisfied by the following lemma which can be trivially proven.

## Lemma 3.1 (Thread Deletion)

If  $\mathbb{Q}$  is well-typed with regard to  $\Theta$ , then for all  $t \in \mathbb{Q}$  we know  $\mathbb{Q} \setminus \{t\}$  is well-typed with regard to  $\Theta \setminus \{t\}$ .

For the "fork" instruction, things are trickier. We need to ensure that the new child thread does not interfere with threads in the parent thread's environment. We also require that the parent thread does not interfere with the child thread. The following lemma ensures the first requirement.

## Lemma 3.2 (Queue Extension I)

Suppose  $\mathbb Q$  is well-typed with regard to  $\Theta$  and the current executing thread is t. If

- $\Theta(t) = (A, G);$

- a new thread t' is created by t;

- (A', G') is the instantiation of the corresponding static thread specification by the thread argument;

- $A \Rightarrow A'$  and  $G' \Rightarrow G;$

then  $\mathbb{Q}' \cup \{t'\}$  is well-typed with regard to  $\Theta'\{t' \rightsquigarrow (A', G')\}$ , where  $\mathbb{Q}' = \mathbb{Q} \setminus \{t\}$  and  $\Theta' = \Theta \setminus \{t\}$ .

Here  $\mathbb{Q}'$  is the environment of the current thread t. Since t does not interfere with its environment (because  $\mathbb{Q}$  is well-typed), we know that its assumption A is an approximation of what the environment can guarantee ( $G_e$ ), and similarly that G is an approximation of the environment's assumption ( $A_e$ ). By this interpretation, we can unify the concepts of the current running thread's assumption/guarantee with its environment's guarantee/assumption. To ensure the new thread t' does not interfere with t's environment, we need  $G' \Rightarrow A_e$  and  $G_e \Rightarrow A'$ , which can be derived from  $G' \Rightarrow G$ and  $A \Rightarrow A'$ .

Still, we need to ensure that thread t does not interfere with t'. As mentioned above, A and G are approximations of  $G_e$  and  $A_e$ , respectively. Since the environment is extended with the child thread, the guarantee  $G'_e$  for the new environment is  $G_e \vee G'$  and the assumption for the new environment  $A'_e$  is  $A_e \wedge A'$ . We want to change A and G correspondingly to reflect the environment change. First, the following lemma says that the specification of a dynamic thread can be changed during its lifetime.

#### Lemma 3.3 (Queue Update)

Suppose  $\mathbb{Q}$  is well-typed with regard to  $\Theta$  and that the current executing thread is t. If

$<sup>^2</sup>$  This is a temporary formulation to illustrate our basic idea. We will use different definitions in our formal development of CMAP in Section 4.

- $\Theta(t) = (A, G);$

- $G'' \Rightarrow G$  and  $A \Rightarrow A'';$

• the subsequent behavior of the current thread satisfies  $(A^{\prime\prime},G^{\prime\prime});$

then  $\mathbb{Q}$  is well-typed with regard to  $\Theta\{t \rightsquigarrow (A'', G'')\}$ .

Now we can change the specification of the parent thread t to let it reflect the change of the environment.

# Lemma 3.4 (Queue Extension II)

Suppose  $\mathbb{Q}$  is well-typed with regard to  $\Theta$  and the current executing thread is t. If

- $\Theta(t) = (A, G);$

- a new thread t' is created by t;

- (A', G') is the instantiation of the corresponding static thread specification by the thread argument;

- $(A \Rightarrow A') \land (G' \Rightarrow G);$

- the remainder behavior of the thread t also satisfies  $(A \lor G', G \land A')$ ;

then  $\mathbb{Q} \cup \{t'\}$  is well-typed with regard to  $\Theta\{t' \rightsquigarrow (A', G'), t \rightsquigarrow (A \lor G', G \land A')\}.$

If t later creates another thread t", because the specification of t already reflects the existence of t', by Lemma 3.2 we know that t" will not interfere with t' as long as its specification satisfies the constraints. Therefore we do not need to explicitly check that t' and t" are activated from the same static thread or that multiple activations of a static thread do not interfere with each other.

These lemmas are used to prove the soundness of CMAP. They are somewhat similar to the heap update and heap extension lemmas used in TAL's soundness proof [27]. People familiar with the traditional rely-guarantee method may feel this is nothing but the parallel composition rule used to support nested **cobegin/coend**. However, by combining the invariant-based proof technique used by type systems and the traditional rely-guarantee method, we can now verify multi-threaded assembly program with a more flexible program structure than the **cobegin/coend** structure. In particular, programs which are not properly nested, as shown in Figure 4(c) and the main2 program in Figure 3, can be supported in our system. This is one of the most important contributions of this paper.

#### 3.2 Parameterized Assumption/Guarantee

The assumptions and guarantees are interfaces between threads, which should only talk about shared resources. As we allow multiple activations of static threads, the behavior of a dynamic thread may depend on its arguments, which is the thread's private data. Therefore, to specify a static thread, the assumption and guarantee need to be parameterized over the thread argument.

In our thread model, the flat memory space is shared by all threads, and as in most operating systems, the register file is saved at the moment of context switch. Therefore the register file is thread-private data. The thread argument is stored in a dedicated register.

Rather than letting the assumption and guarantee be parameterized over the thread argument, we let them be parameterized over the whole register file. This makes our specification language very expressive. For instance, we allow the dynamic thread to change its specification during its lifetime to reflect change in the environment. If the thread has private data that tracks the composition of the environment, and its specification is parameterized by such data, then its specification automatically changes with the change of the data, which in turn results from the change of the thread environment. This is the key technique we use to support unbounded dynamic thread creation, as shown in the program main2 in Figure 3.

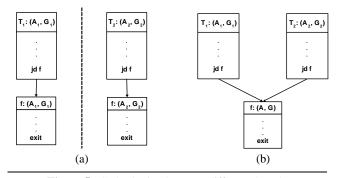

Figure 5. Code sharing between different threads

# 3.3 Support of Modular Verification

The rely-guarantee method supports thread modularity well, *i.e.*, code of one thread can be verified independently without inspecting other threads' code. However, it does not have good support for code reuse. In CCAP, each thread has its own code heap and there is no sharing of code between threads. As Figure 5(a) shows, if an instruction sequence is used by multiple threads, it has multiple copies in different threads' code heaps, each copy verified with regard to the specifications of these threads.

Based on the rely-guarantee method, the thread modularity is also supported in our system. In addition, using our "lazy" checking of thread non-interference, and by the queue update lemma, we can allow instruction sequences to be specified independently of their calling thread, thus achieving better modularity.

As shown in Figure 5(b), we assign an assumption/guarantee pair to the specification of each instruction sequence, and require the instruction sequence be well-behaved with regard to its own assumption/guarantee. Similar to threads, the instruction sequence is well-behaved if, when it is executed by a dynamic thread, its execution is safe and satisfies its guarantee, as long as other dynamic threads in the environment satisfy the assumption. The instruction sequence only needs to be verified once with respect to its own specification, and can be executed by different threads as long as certain constraints are satisfied.

Intuitively, it is safe for a dynamic thread t with specification  $(A_i, G_i)$  to execute the instruction sequence labeled by f as long as executing it does not require a stronger assumption than  $A_i$ , nor does it violate the guarantee  $G_i$ . Therefore, if the specification of f is (A, G), t can call f as long as  $A_i \Rightarrow A$  and  $G \Rightarrow G_i$ . The intuition is backed up by our queue update lemma.

# 4. CMAP

The language CMAP is based on an "untyped" low-level abstract machine supporting multi-threaded programs with dynamic thread creation and argument passing. The "type" system of CMAP uses the calculus of inductive constructions (CiC) [32] to essentially support reasoning in higher-order predicate logic.

#### 4.1 The Abstract Machine

Figure 6 shows the definition of our abstract machine.

A CMAP program (corresponding to a complete machine state) is made up of an updatable state  $\mathbb{S}$  (which is made up of the shared memory  $\mathbb{M}$  and the register file  $\mathbb{R}$ ), a dynamic thread queue  $\mathbb{Q}$ , two shared code heaps  $\mathbb{C}$  (for basic code blocks) and  $\mathbb{T}$  (for thread entries), and the current instruction sequence  $\mathbb{I}$  of the currently executing thread. Here  $\mathbb{C}$  and  $\mathbb{T}$  can be merged, but conceptually it is cleaner to have them separated because the specification of  $\mathbb{T}$  and is different from that of  $\mathbb{C}$  (See Section 4.3: for  $\mathbb{T}$  we do not need to specify a local guarantee). Memory is a partial mapping from

| $((\mathbb{M},\mathbb{R}),\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I})\longmapsto\mathbb{P}$ |                                                                                                                                                                                                                                       |  |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| if $\mathbb{I} =$                                                                            | then $\mathbb{P} =$                                                                                                                                                                                                                   |  |

| fork h, r; $\mathbb{I}''$                                                                    | $((\mathbb{M},\mathbb{R}),\mathbb{Q}\{t\rightsquigarrow (\mathbb{R}',\mathbb{I}')\},\mathbb{T},\mathbb{C},\mathbb{I}'')$                                                                                                              |  |

|                                                                                              | where $\mathbb{I}' = \mathbb{T}(h), t \notin dom(\mathbb{Q}), t \neq \mathbb{R}(rt), and \mathbb{R}' = \{r_0 \rightsquigarrow \neg, \ldots, r_{15} \rightsquigarrow \neg, rt \rightsquigarrow t, ra \rightsquigarrow \mathbb{R}(r)\}$ |  |

| yield; $\mathbb{I}''$                                                                        | $((\mathbb{M},\mathbb{R}'),(\mathbb{Q}\{\mathbb{R}(rt)\rightsquigarrow(\mathbb{R},\mathbb{I}'')\})\setminus\{t\},\mathbb{T},\mathbb{C},\mathbb{I}')$                                                                                  |  |

|                                                                                              | where $t \in dom(\mathbb{Q})$ and $(\mathbb{R}', \mathbb{I}') = \mathbb{Q}(t)$ or $t = \mathbb{R}(rt)$ and $(\mathbb{R}', \mathbb{I}') = (\mathbb{R}, \mathbb{I}'')$                                                                  |  |

| exit                                                                                         | $((\mathbb{M},\mathbb{R}'),\mathbb{Q}\setminus\{t\},\mathbb{T},\mathbb{C},\mathbb{I}')$ where $t\in dom(\mathbb{Q})$ and $(\mathbb{R}',\mathbb{I}')=\mathbb{Q}(t)$                                                                    |  |

| jd f                                                                                         | $((\mathbb{M},\mathbb{R}),\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I}') \qquad 	ext{ where } \mathbb{I}'=\mathbb{C}(\mathtt{f})$                                                                                                      |  |

| $bgt\mathtt{r}_s,\mathtt{r}_t,\mathtt{f};\mathbb{I}''$                                       | $((\mathbb{M},\mathbb{R}),\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I}'')$ if $\mathbb{R}(r_s) \leq \mathbb{R}(r_t),$                                                                                                                  |  |

|                                                                                              | $((\mathbb{M}, \mathbb{R}), \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I}')$ otherwise, where $\mathbb{I}' = \mathbb{C}(f)$                                                                                                          |  |

| $beq\mathtt{r}_s,\mathtt{r}_t,\mathtt{f};\mathbb{I}''$                                       | $((\mathbb{M},\mathbb{R}),\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I}'')$ if $\mathbb{R}(r_s) \neq \mathbb{R}(r_t),$                                                                                                                  |  |

|                                                                                              | $((\mathbb{M}, \mathbb{R}), \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I}')$ otherwise, where $\mathbb{I}' = \mathbb{C}(f)$                                                                                                          |  |

| $c; \mathbb{I}''$ for remaining                                                              | $(Next(c,(\mathbb{M},\mathbb{R})),\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I}')$                                                                                                                                                      |  |

| cases of c                                                                                   |                                                                                                                                                                                                                                       |  |

Figure 8. Operational semantics of CMAP

| (Program)  | $\mathbb{P}$ | $::=(\mathbb{S},\mathbb{Q},\mathbb{T},\mathbb{C},\mathbb{I})$                                                                       |

|------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|

| (State)    | S            | $::=(\mathbb{M},\mathbb{R})$                                                                                                        |

| (Memory)   | $\mathbb{M}$ | $::= \{1 \rightarrow w\}^*$                                                                                                         |

| (RegFile)  | $\mathbb{R}$ | $::= \{r \rightsquigarrow w\}^*$                                                                                                    |

| (Register) | r            | $::= r_0   r_1   \dots   r_{15}   rt   ra$                                                                                          |

| (CdHeap)   | $\mathbb{C}$ | $::= \{f \rightsquigarrow \mathbb{I}\}^*$                                                                                           |

| (Labels)   | f,1          | ::=n (nat nums)                                                                                                                     |

| (WordVal)  | W            | ::=n (nat nums)                                                                                                                     |

| (TEntries) | Τ            | $::= \{h \rightsquigarrow \mathbb{I}\}^*$                                                                                           |

| (TQueue)   | $\mathbb{Q}$ | $::= \{t \rightsquigarrow (\mathbb{R}, \mathbb{I})\}^*$                                                                             |

| (THandles) | h            | ::=n (nat nums)                                                                                                                     |

| (ThrdID)   | t            | ::=n (nat nums)                                                                                                                     |

| (InstrSeq) | $\mathbb{I}$ | ::= c; I ∣ jd f ∣ exit                                                                                                              |

| (Commd)    | С            | ::= yield   fork h, r   add r <sub>d</sub> , r <sub>s</sub> , r <sub>t</sub>   sub r <sub>d</sub> , r <sub>s</sub> , r <sub>t</sub> |

|            |              | $  movi r_d, w   bgt r_s, r_t, f   beq r_s, r_t, f$                                                                                 |

|            |              | $ \operatorname{Id} \mathtt{r}_d, \mathtt{r}_s(\mathtt{w})  \operatorname{st} \mathtt{r}_d(\mathtt{w}), \mathtt{r}_s$               |

Figure 6. The abstract machine

| if c =                                                     | then $	ext{Next}(	ext{c},(\mathbb{M},\mathbb{R})) =$                                                            |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| add $r_d, r_s, r_t$                                        | $(\mathbb{M}, \mathbb{R}\{\mathtt{r}_d \rightsquigarrow \mathbb{R}(\mathtt{r}_s) + \mathbb{R}(\mathtt{r}_t)\})$ |

| $sub\mathtt{r}_d,\mathtt{r}_s,\mathtt{r}_t$                | $(\mathbb{M}, \mathbb{R}\{\mathbf{r}_d \rightsquigarrow \mathbb{R}(\mathbf{r}_s) - \mathbb{R}(\mathbf{r}_t)\})$ |

| movir <sub>d</sub> ,w                                      | $(\mathbb{M}, \mathbb{R}\{\mathtt{r}_d \rightsquigarrow \mathtt{w}\})$                                          |

| $Id\mathtt{r}_d,\mathtt{r}_s(\mathtt{w})$                  | $(\mathbb{M}, \mathbb{R}\{\mathbf{r}_d \rightsquigarrow \mathbb{M}(\mathbb{R}(\mathbf{r}_s) + \mathbf{w})\})$   |

|                                                            | where $(\mathbb{R}(\mathbf{r}_s) + \mathbf{w}) \in dom(\mathbb{M})$                                             |

| $\operatorname{St} \mathtt{r}_d(\mathtt{w}), \mathtt{r}_s$ | $(\mathbb{M}\{(\mathbb{R}(\mathtt{r}_d) + \mathtt{w}) \rightsquigarrow \mathbb{R}(\mathtt{r}_s)\}, \mathbb{R})$ |

|                                                            | where $(\mathbb{R}(\mathbf{r}_d) + \mathbf{w}) \in dom(\mathbb{M})$                                             |

Figure 7. Auxiliary state update function

memory locations to word-sized values. The register file  $\mathbb{R}$  maps registers to word-sized values. In our machine, there are 16 general purpose registers ( $r_0 - r_{15}$ ) and two special registers (rt and ra) that hold the current thread id and the thread argument. Code heaps map code labels to instruction sequences, which are lists of instructions terminated by a jd or exit instruction. Code labels pointing to thread entries are also called *thread handles*.  $\mathbb{T}$  maps thread handles to thread entries (instruction sequences from which a thread starts to execute). Thread entries are also called *static threads*. The current instruction sequence  $\mathbb{I}$  plays the role of the program counter of the current executing thread.

For simplicity, we just model the queue of ready threads, which is the dynamic thread queue  $\mathbb{Q}$  that maps the dynamic thread id to an execution context of a thread. The dynamic thread id t is a natural number generated randomly at run time. The thread execution context includes the snapshot of the register file and the program point where the thread will resume its execution. Note that  $\mathbb{Q}$  does not contain the current executing thread, which is different from the dynamic thread queue used in Section 3. The instruction set of CMAP just contains the most basic and common assembly instructions. It also includes primitives fork, exit and yield to support multi-threaded programming which can be viewed as system calls to a thread library. We do not have a join instruction because thread join can be implemented using synchronization. Readers who are eager to see a CMAP program can take a quick look at Figure 10 in Section 5.1 (ignore the specifications and annotations in program for the time being), which is the CMAP implementation of programs main2 and chld shown in Figure 3.

The execution of CMAP programs is modeled as small-step transitions from one program to another, *i.e.*,  $\mathbb{P} \mapsto \mathbb{P}'$ . Figure 8 defines the program transition function.

The primitive fork creates a new thread using the static thread h, and passes the value  $\mathbb{R}(r)$  to it as the argument. The new thread will be assigned a fresh thread id and placed in the dynamic thread queue waiting for execution. The current thread continues with the subsequent instructions.

At a yield instruction, the current thread will give up the control of the machine. Its execution context is stored in  $\mathbb{Q}$ . The scheduler will pick one thread non-deterministically from the thread queue (which might be the yielding thread itself), restore its execution context, and execute it.

The exit instruction terminates the execution of the current thread and non-deterministically selects a thread from the thread queue. Here we have the implicit assumption that there is always an idle thread in the thread queue that never changes the state or terminates, ensuring that the thread queue will never be empty.

Semantics for the rest of the instructions are standard. The "next state" function defined in Figure 7 describes the effects of some instructions on the state.

#### 4.2 The Meta-Logic

To encode the specification and proofs, we use the calculus of inductive constructions (CiC) [37, 32], which is an extension of the calculus of constructions (CC) [7] with inductive definitions. CC corresponds to Church's higher-order predicate logic via the Curry-Howard isomorphism.

CiC has been shown strongly normalizing [38], hence the corresponding logic is consistent. It is supported by the Coq proof assistant [37], which we have used to implement CMAP.

In the remainder of this paper, we will mainly use the more familiar mathematical and logical notations, instead of strict CiC or Coq representation. We use *Prop* to denote the type of all propositions. No knowledge of CiC and Coq is required to understand them.

#### 4.3 Program Specifications

The verification constructs of CMAP are defined in Figure 9. The program specification  $\Phi$  is a global invariant (*Inv*), a static thread

| (ProgSpec)<br>(ThrdSpec)<br>(ThrdType)<br>(CdHpSpec)<br>(ActTSpec) | $\begin{split} \Phi & ::= (\mathit{Inv}, \Delta, \Psi) \\ \Delta & ::= \{h \rightsquigarrow \theta\}^* \\ \theta & ::= (p, \mathbb{A}, \mathbb{G}) \\ \Psi & ::= \{f \rightsquigarrow (p, g, \mathbb{A}, \mathbb{G})\}^* \\ \Theta & ::= \{t \rightsquigarrow (p, \mathbb{A}, \mathbb{G})\}^* \end{split}$ |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Invariant)<br>(Assertion)<br>(Assumption)<br>(Guarantee)          | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                       |

Figure 9. Verification constructs of CMAP

specification  $\Delta$ , and a code heap specification  $\Psi$ . The invariant *Inv* is a programmer specified predicate, which implies a safety property of concern. It must hold throughout the execution of the program. The static thread specification  $\Delta$  contains a specification  $\theta$  for each static thread in  $\mathbb{T}$ . Each  $\theta$  contains a precondition p to invoke this thread, and an assumption  $\mathbb{A}$  and guarantee  $\mathbb{G}$  for this thread with regard to the environment at its creation time.

A code heap specification  $\Psi$  assigns a quadruple (p, g, A, G) to each instruction sequence. The assertion p is the precondition to execute the code sequence. The local guarantee g, as introduced in Section 2.2, describes a valid state transition – it is safe for the current thread to yield control only after making a state transition described by g. As explained in Section 3.3,, we assign a pair of A and G to each instruction sequence as part of its specification. The instruction sequence can be verified with regard to its own specification without knowing which thread executes it. Here the A and G reflect knowledge of the dynamic thread environment at the time the instruction sequence is executed.

The global invariant *Inv* is a CiC term of type  $Mem \rightarrow Prop$ , *i.e.*, a predicate over memory. *Inv* does not specify the register file, which contains thread-private data and keeps changing. In contrast to *Inv*, assertions (p) are predicates over the whole state. Assumptions and guarantees (*e.g.*, A, G and g) are CiC terms with type *RegFile*  $\rightarrow Mem \rightarrow Mem \rightarrow Prop$ , which means predicates over a register file and two instances of memory. Assumptions and guarantees specify the behavior of threads by describing the change of shared memory. As mentioned in Section 3.2, they are parameterized over the register file, which contains the private data of threads.

We also define the specification  $\Theta$  of active threads in the thread queue  $\mathbb{Q}$ . Within  $\Theta$ , each triple  $(p, \mathbb{A}, \mathbb{G})$  describes a dynamic thread at its yield point (or at the beginning if it has just forked). The assertion p gives the constraint of the state when the thread gets control back to execute its remaining instructions. The assumption and guarantee used by the thread at the yield point are given by  $\mathbb{A}$ and  $\mathbb{G}$ . As we said in Section 3.1, the  $\mathbb{A}$  and  $\mathbb{G}$  of each dynamic thread may change during the lifetime of the thread. Notice that  $\Theta$  is not part of the program specification. It is used only in the soundness proof.

## 4.4 Inference Rules

We use the following judgement forms to define the inference rules:

| $\Phi; \Theta; (p, g, \mathbb{A}, \mathbb{G}) \vdash \mathbb{P}$ | (well-formed program)         |

|------------------------------------------------------------------|-------------------------------|

| $\Phi; \Theta; (g, \mathbb{S}) \vdash \mathbb{Q}$                | (well-formed dynamic threads) |

| $\Phi \vdash \mathbb{T}$                                         | (well-formed static threads)  |

| $\Phi \vdash \mathbb{C}$                                         | (well-formed code heap)       |

| $\Phi$ ; (p, g, A, G) $\vdash \mathbb{I}$                        | (well-formed instr. sequence) |

Before introducing the inference rules, we first define some shorthands in Table 1 to simplify our presentation.

*Well-formed programs.* The PROG rule shows the invariants that need to be maintained during program transitions.

| Representation                                                                          | Defi nition                                                                                                                                                                                 |

|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| S(r)                                                                                    | $\mathbb{R}(r)$ where $\mathbb{S}=(\mathbb{M},\mathbb{R})$                                                                                                                                  |

| $Inv \wedge p$                                                                          | $\lambda(\mathbb{M},\mathbb{R}).$ Inv $\mathbb{M}\wedge p(\mathbb{M},\mathbb{R})$                                                                                                           |

| gSM′                                                                                    | g $\mathbb{R} \mathbb{M} \mathbb{M}'$ , where $\mathbb{S} = (\mathbb{M}, \mathbb{R})$                                                                                                       |

| A S M', G S M'                                                                          | similar to g $\mathbb{S} \mathbb{M}'$                                                                                                                                                       |

| poc                                                                                     | $\lambda \mathbb{S}.p(\texttt{Next}(\texttt{c},\mathbb{S}))$                                                                                                                                |

| goc                                                                                     | $\lambda \mathbb{S}. \lambda \mathbb{M}'. g (\operatorname{Next}(c, \mathbb{S})) \mathbb{M}'$                                                                                               |

| A∘c, G∘c                                                                                | similar to $g \circ c$                                                                                                                                                                      |

| $p \Rightarrow p'$                                                                      | $\forall \mathbb{S}. \mathbf{p} \ \mathbb{S} \Rightarrow \mathbf{p}' \ \mathbb{S}$                                                                                                          |

| $p \Rightarrow g$                                                                       | $\forall \mathbb{R}, \mathbb{M}.p \ (\mathbb{M}, \mathbb{R}) \Rightarrow g \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}$                                                                          |

| $p \Rightarrow g \Rightarrow g'$                                                        | $\forall \mathbb{S}, \mathbb{M}'. p \ \mathbb{S} \Rightarrow g \ \mathbb{S} \ \mathbb{M}' \Rightarrow g' \ \mathbb{S} \ \mathbb{M}'$                                                        |

| $\mathbb{A} \Rightarrow \mathbb{A}'$                                                    | $\forall \mathbb{R}, \mathbb{M}, \mathbb{M}'.\mathbb{A} \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}' \Rightarrow \mathbb{A}' \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}'$                            |

| $\mathbb{G} \Rightarrow \mathbb{G}'$                                                    | $\forall \mathbb{R}, \mathbb{M}, \mathbb{M}'.\mathbb{G} \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}' \Rightarrow \mathbb{G}' \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}'$                            |

| $p \stackrel{\mathbb{R}}{\Longrightarrow} g \stackrel{\mathbb{R}'}{\Longrightarrow} p'$ | $\forall \mathbb{M}, \mathbb{M}'. \texttt{p} \ (\mathbb{M}, \mathbb{R}) \Rightarrow \texttt{g} \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}' \Rightarrow \texttt{p} \ (\mathbb{M}', \mathbb{R}')$ |

| $(\mathit{Inv}, \texttt{p} \circlearrowleft \mathbb{A}, \mathbb{R})$                    | $(Inv \land p) \stackrel{\mathbb{R}}{\Longrightarrow} \mathbb{A} \stackrel{\mathbb{R}}{\Longrightarrow} p$                                                                                  |

Table 1. Assertion definitions and syntactic sugar

| $(Inv, \Delta, \Psi) = \Phi$                                                                                       | $(\mathbb{M},\mathbb{R})=\mathbb{S}$ $t=\mathbb{R}(rt)$                                                                                                  |        |  |

|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

| $\Phi \vdash \mathbb{T}  \Phi \vdash \mathbb{C}$                                                                   | $(Inv \land p) \mathbb{S}  \Phi; (p, g, \mathbb{A}, \mathbb{G}) \vdash \mathbb{I}$                                                                       |        |  |

| $\Phi;\Theta;(g,\mathbb{S})\vdash\mathbb{Q}$                                                                       | $\frac{(mv \land p) }{\mathrm{NI}(\Theta\{t \rightsquigarrow (p, \mathbb{A}, \mathbb{G})\}, \mathbb{Q}\{t \rightsquigarrow (\mathbb{R}, \mathbb{I})\})}$ | (PPOG) |  |

| $\Phi; \Theta; (p, g, \mathbb{A}, \mathbb{G}) \vdash (\mathbb{S}, \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I})$ |                                                                                                                                                          |        |  |

The well-formedness of a program is judged with respect to the program specification  $\Phi$ , the dynamic thread specification  $\Theta$ , and the specification of the current executing thread (p, g, A, G). Compared with the triples in  $\Theta$ , we need the local guarantee g here to specify the transition which the current thread must make before it yields control.

In the first line, we give the composition of the program specification, the current state and the current thread id. Here we use a pattern match representation, which will be used in the rest of this paper.

We require the code, including the thread entry points  $\mathbb{T}$  and the code heap  $\mathbb{C}$ , always be well-formed with respect to the program specification. Since  $\Phi$ ,  $\mathbb{T}$  and  $\mathbb{C}$  do not change during program transitions, the check for the first two premises in line 2 can be done once and for all.

The next premise shows the constraints on the current state S: it must satisfy both the global invariant *Inv* and the assertion p of the current thread. The last premise in line 2 essentially requires it be safe for the current thread to execute the remainder instruction sequence  $\mathbb{I}$ .

Premises in line 3 require the well-formedness of dynamic threads in  $\mathbb{Q}$ , which is checked by the rule DTHRDS, and the non-interference between all the live threads.

*Non-interference.* The non-interference macro  $NI(\Theta, \mathbb{Q})$  requires that each dynamic thread be compatible with all the other. It is formally defined as:

$$\begin{aligned} \forall \mathsf{t}_i, \mathsf{t}_j \in dom(\Theta). \forall \mathbb{M}, \mathbb{M}'. \\ \mathsf{t}_i \neq \mathsf{t}_j \Rightarrow \mathbb{G}_i \ \mathbb{R}_i \ \mathbb{M} \ \mathbb{M}' \Rightarrow \mathbb{A}_j \ \mathbb{R}_j \ \mathbb{M} \ \mathbb{M}', \end{aligned}$$

where  $(-, A_i, \mathbb{G}_i) = \Theta(t_i), (-, A_j, \mathbb{G}_j) = \Theta(t_j), \mathbb{R}_i = \mathbb{Q}(t_i)$ and  $\mathbb{R}_j = \mathbb{Q}(t_j)$ .

As explained in Section 3, here we enforce the non-interference by a lazy check of specifications  $\Theta$  of dynamic threads in  $\mathbb{Q}$ , instead of checking the specification  $\Delta$  of all static threads in  $\mathbb{T}$ .

*Well-formed dynamic threads.* The rule DTHRDS ensures each dynamic thread in  $\mathbb{Q}$  is in good shape with respect to the specification  $\Theta$ , the current program state  $\mathbb{S}$ , and the transition g that the current thread need do before other threads can take control.

$\begin{aligned} (\mathbb{R}_k, \mathbb{I}_k) &= \mathbb{Q}(\mathsf{t}_k), \ (p_k, \mathbb{A}_k, \mathbb{G}_k) = \Theta(\mathsf{t}_k), \ \forall \mathsf{t}_k \in dom(\mathbb{Q}) \\ (\mathit{Inv}, p_k \circlearrowleft \mathbb{A}_k, \mathbb{R}_k) \quad \forall \mathbb{M}'. \mathsf{g} \ \mathbb{R} \ \mathbb{M} \ \mathbb{M}' \Rightarrow \mathsf{p}_k \ (\mathbb{M}', \mathbb{R}_k) \\ (\mathit{Inv}, \Delta, \Psi); (p_k, \mathbb{G}_k, \mathbb{A}_k, \mathbb{G}_k) \vdash \mathbb{I}_k \\ \hline (\mathit{Inv}, \Delta, \Psi); \Theta; (\mathsf{g}, (\mathbb{M}, \mathbb{R})) \vdash \mathbb{Q} \end{aligned}$

(DTHRDS)

The first line gives the specification of each thread when it reaches a yield point, and its execution context.

The first premise in line 2 requires that if it is safe for a thread to take control at certain state, it should be also safe to do so after any state transition satisfying its assumption. Note that the state transition will not affect the thread-private data in  $\mathbb{R}_k$ .

The second premise describes the relationship between the local guarantee of the current thread and the preconditions of other threads. For any transitions starting from the current state  $(\mathbb{M}, \mathbb{R})$ , as long as it satisfies g, it should be safe for other threads to take control at the result state.

Line 3 requires that for each thread its remainder instruction sequence must be well formed. Note we use  $\mathbb{G}_k$  as the local guarantee because after yield, a thread starts a new "atomic transition" described by its global guarantee.

*Well-formed static threads.* This rule checks the static thread entry is well formed with respect to its specification in  $\Delta$ .

$$\begin{array}{l} (\mathbf{p}_{k}, \mathbb{A}_{k}, \mathbb{G}_{k}) = \Delta(\mathbf{h}_{k}), \ \mathbb{I}_{k} = \mathbb{T}(\mathbf{h}_{k}), \ \forall \mathbf{h}_{k} \in dom(\mathbb{T}) \\ \\ \frac{\forall \mathbb{R}.(\mathit{Inv}, \mathbf{p}_{k} \oslash \mathbb{A}_{k}, \mathbb{R}) \quad (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}_{k}, \mathbb{G}_{k}, \mathbb{A}_{k}, \mathbb{G}_{k}) \vdash \mathbb{I}_{k}}{(\mathit{Inv}, \Delta, \Psi) \vdash \mathbb{T}} \\ \end{array}$$

$$(THRDS)$$

The first line gives the specification for each static thread in  $\mathbb{T}$ . We implicitly require  $dom(\Delta) = dom(\mathbb{T})$ .

The first premise in line 2 says that if it is safe to invoke the new thread at certain state, it should also be safe to delay the invocation after any transition satisfying the assumption of this thread.

The initial instruction sequence of each thread must be wellformed with respect to the thread specification. This is required by the last premise.

*Well-formed code heap.* A code heap is well formed if every instruction sequence is well-formed with respect to its corresponding specification in  $\Psi$ .

$$\frac{dom(\Psi) = dom(\mathbb{C}) \quad (Inv, \Delta, \Psi); \Psi(f) \vdash \mathbb{C}(f), \forall f \in dom(\Psi)}{(Inv, \Delta, \Psi) \vdash \mathbb{C}}$$

(CDHP)

*Thread creation.* The FORK rule describes constraints on new thread creation, which enforces the non-interference between the new thread and existing threads.

$$\begin{split} (\mathbf{p}', \mathbb{A}', \mathbb{G}') &= \Delta(\mathbf{h}) \\ \mathbb{A} \Rightarrow \mathbb{A}'' \quad \mathbb{G}'' \Rightarrow \mathbb{G} \quad (\mathbb{A} \lor \mathbb{G}'') \Rightarrow \mathbb{A}' \quad \mathbb{G}' \Rightarrow (\mathbb{G} \land \mathbb{A}'') \\ \forall \mathbb{R}, \mathbb{R}'. \ (\mathbb{R}(\mathsf{rt}) \neq \mathbb{R}'(\mathsf{rt}) \land \mathbb{R}(\mathbf{r}) = \mathbb{R}'(\mathsf{ra})) \Rightarrow ((\mathit{Inv} \land \mathbf{p}) \stackrel{\mathbb{R}}{\Longrightarrow} \mathsf{g} \stackrel{\mathbb{R}'}{\Longrightarrow} \mathsf{p}') \\ \underbrace{(\mathit{Inv}, \Delta, \Psi); (\mathbf{p}, \mathsf{g}, \mathbb{A}'', \mathbb{G}'') \vdash \mathbb{I}}_{(\mathit{Inv}, \Delta, \Psi); (\mathbf{p}, \mathsf{g}, \mathbb{A}, \mathbb{G}) \vdash \mathsf{fork} \mathsf{h}, \mathsf{r}; \mathbb{I}}_{(\mathsf{FORK})} \end{split}$$

As explained in Section 3.1, the parent thread can change its specification to reflect the change of the environment. To maintain the non-interference invariant, constraints between specifications of the parent and child threads have to be satisfied, as described in Lemma 3.4. Here we enforce these constraints by premises in line 2, where  $(\mathbb{A} \vee \mathbb{G}'') \Rightarrow \mathbb{A}'$  is the shorthand for:

$$\begin{array}{l} \forall (\mathbb{M}, \mathbb{R}). \forall \mathbb{M}', \mathbb{M}''. \forall \mathbb{R}'. (\mathit{Inv} \land p) \ (\mathbb{M}, \mathbb{R}) \Rightarrow \mathbb{R}(\mathsf{rt}) \neq \mathbb{R}'(\mathsf{rt}) \\ \Rightarrow \mathbb{R}(\mathsf{r}) = \mathbb{R}'(\mathsf{ra}) \Rightarrow (\mathbb{A} \lor \mathbb{G}'') \mathbb{R} \ \mathbb{M}' \ \mathbb{M}'' \Rightarrow \mathbb{A}' \ \mathbb{R}' \ \mathbb{M}' \ \mathbb{M}'', \end{array}$$

and  $\mathbb{G}' \Rightarrow (\mathbb{G} \land \mathbb{A}'')$  for:

$\begin{array}{l} \forall (\mathbb{M},\mathbb{R}).\forall \mathbb{M}',\mathbb{M}''.\forall \mathbb{R}'.(\mathit{Inv} \land p) \ (\mathbb{M},\mathbb{R}) \Rightarrow \mathbb{R}(\mathsf{rt}) \neq \mathbb{R}'(\mathsf{rt}) \\ \Rightarrow \mathbb{R}(\mathsf{r}) = \mathbb{R}'(\mathsf{ra}) \Rightarrow \mathbb{G}' \ \mathbb{R}' \ \mathbb{M}' \ \mathbb{M}'' \Rightarrow (\mathbb{G} \land \mathbb{A}'') \ \mathbb{R} \ \mathbb{M}' \ \mathbb{M}''. \end{array}$

Above non-interference checks use the extra knowledge that:

- the new thread id is different with its parent's, *i.e.*,  $\mathbb{R}(\mathsf{rt}) \neq \mathbb{R}'(\mathsf{rt})$ ;

- the argument of the new thread comes from the parent's register r, *i.e.*, ℝ(r) = ℝ'(ra);

- the parent's register file satisfies the precondition, *i.e.*,  $(Inv \land p)$  ( $\mathbb{M}, \mathbb{R}$ ).

In most cases, the programmer can just pick  $(\mathbb{A} \vee \widehat{\mathbb{G}}')$  and  $(\mathbb{G} \land \widehat{\mathbb{A}}')$  as  $\mathbb{A}''$  and  $\mathbb{G}''$  respectively, where  $\widehat{\mathbb{G}}'$  and  $\widehat{\mathbb{A}}'$  are instantiations of  $\mathbb{G}'$  and  $\mathbb{A}'$  using the value of the child's argument.

The premise in line 3 says that after the current thread completes the transition described by g, it should be safe for the new thread to take control with its new register file ( $\mathbb{R}'$ ), whose relationship between the parents register file  $\mathbb{R}$  is satisfied.

The last premise checks the well-formedness of the remainder instruction sequence. Since the fork instruction does not change states, we need not change the precondition p and g.

# Yielding and termination.

$$\frac{\forall \mathbb{R}. (Inv, p \circlearrowright \mathbb{A}, \mathbb{R}) \quad (Inv \land p) \Rightarrow g \quad (Inv, \Delta, \Psi); (p, \mathbb{G}, \mathbb{A}, \mathbb{G}) \vdash \mathbb{I} }{(Inv, \Delta, \Psi); (p, g, \mathbb{A}, \mathbb{G}) \vdash \mathsf{yield}; \mathbb{I} }$$

(YIELD)

The YIELD rule requires that it is safe for the yielding thread to take back control after any state transition satisfying the assumption  $\mathbb{A}$ . Also the current thread cannot yield until it completes the required state transition, *i.e.*, an identity transition satisfies the local guarantee g. Lastly, one must verify the remainder instruction sequence with the local guarantee reset to  $\mathbb{G}$ .

$$\frac{(Inv \land p) \Rightarrow g}{(Inv, \Delta, \Psi); (p, g, \mathbb{A}, \mathbb{G}) \vdash \mathsf{exit}}$$

(EXIT)

The rule EXIT is simple: it is safe for the current thread to terminate its execution only after it finishes the required transition described by g, which is an identity transition.

#### Type-checking other instructions.

$$c \in \{ \operatorname{add} r_d, r_s, r_t, \operatorname{sub} r_d, r_s, r_t, \operatorname{movi} r_d, w\}, r_d \notin \{ \operatorname{rt}, \operatorname{ra} \} \\ (\operatorname{Inv} \land p) \Rightarrow (\operatorname{Inv} \land p') \circ c \quad (\operatorname{Inv} \land p) \Rightarrow (g' \circ c) \Rightarrow g \\ \underline{\mathbb{A}} \Rightarrow \underline{\mathbb{A}' \circ c} \quad \underline{\mathbb{G}' \circ c} \Rightarrow \underline{\mathbb{G}} \quad (\operatorname{Inv}, \Delta, \Psi); (p', g', \underline{\mathbb{A}'}, \underline{\mathbb{G}'}) \vdash \mathbb{I} \\ \hline (\operatorname{Inv}, \Delta, \Psi); (p, g, \underline{\mathbb{A}}, \underline{\mathbb{G}}) \vdash c; \mathbb{I}$$

(SIMP)

The rule SIMP covers the verification of instruction sequences starting with a simple command such as add, sub or movi. We require that the program not update registers rt and ra. In these cases, one must find an intermediate precondition  $(p', g', \mathbb{A}', \mathbb{G}')$  under which the remainder instruction sequence I is well-formed.

The global invariant *Inv* and the intermediate assertion p' must hold on the updated machine state, and the intermediate guarantee g' applied to the updated machine state must be no weaker than the current guarantee g applied to the current state.

Since  $\mathbb{A}$  and  $\mathbb{G}$  are parameterized over  $\mathbb{R}$ , which will be changed by the instruction c, one may change  $\mathbb{A}$  and  $\mathbb{G}$  to ensure the assumption does not become stronger and the guarantee does not become weaker.

$$\begin{array}{l} (\mathbf{p}',\mathbf{g}',\mathbb{A}',\mathbb{G}') = \Psi(\mathbf{f}) \\ \hline (\mathit{Inv} \wedge \mathbf{p}) \Rightarrow \mathbf{p}' \quad (\mathit{Inv} \wedge \mathbf{p}) \Rightarrow \mathbf{g}' \Rightarrow \mathbf{g} \quad \mathbb{A} \Rightarrow \mathbb{A}' \quad \mathbb{G}' \Rightarrow \mathbb{G} \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}, \mathbf{g}, \mathbb{A}, \mathbb{G}) \vdash \mathsf{jd} \ \mathbf{f} \end{array}$$

(JD)

The JD rule checks the specification of the target instruction sequence. As mentioned before, each instruction sequence can have its own specification, independent of the thread that will jump to it. It is safe for a thread to execute an instruction sequence as long as executing the instruction sequence does not require a stronger assumption than the thread's assumption  $\mathbb{A}$ , nor does it break the guarantee  $\mathbb{G}$  of the thread.

Inference rules for memory operations are quite similar to the SIMP rule. Here we also need ensure the memory address is in the domain of the data heap.

$$\begin{split} \mathbf{c} &= \mathsf{Id}\,\mathbf{r}_d, \mathbf{r}_s(\mathsf{W}) \quad \mathbf{r}_d \notin \{\mathsf{rt}, \mathsf{ra}\}\\ \forall \mathbb{M}, \forall \mathbb{R}. (\mathit{Imv} \land p) \; (\mathbb{M}, \mathbb{R}) \Rightarrow ((\mathbb{R}(\mathbf{r}_s) + \mathsf{w}) \in \mathit{dom}(\mathbb{M}))\\ (\mathit{Inv} \land p) \Rightarrow (\mathit{Inv} \land p') \circ c \quad (\mathit{Inv} \land p) \Rightarrow (\mathit{g'} \circ c) \Rightarrow \mathsf{g}\\ \forall \mathbb{S}, \mathbb{M}, \mathbb{M}'. \mathbb{A} \; (\mathbb{S}.\mathbb{R}) \; \mathbb{M} \; \mathsf{M'} \Rightarrow \mathbb{A}' \; (\mathsf{Next}(c, \mathbb{S}).\mathbb{R}) \; \mathbb{M} \; \mathsf{M'} \\ \forall \mathbb{S}, \mathbb{M}, \mathbb{M}'. \mathcal{G}' \; (\mathsf{Next}(c, \mathbb{S}).\mathbb{R}) \; \mathbb{M} \; \mathsf{M'} \Rightarrow \mathbb{G} \; (\mathbb{S}.\mathbb{R}) \; \mathbb{M} \; \mathsf{M'} \\ (\mathit{Inv}, \Delta, \Psi); (\mathsf{p'}, \mathsf{g'}, \mathbb{A}', \mathbb{G}') \vdash \mathbb{I} \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathsf{p}, \mathsf{g}, \mathbb{A}, \mathbb{G}) \vdash \mathsf{c}; \mathbb{I} \end{split}$$

(LD)

$$\forall \mathbb{M}, \forall \mathbb{R}. (Inv \land p) \ (\mathbb{M}, \mathbb{R}) \Rightarrow ((\mathbb{R}(\mathbf{r}_d) + \mathbf{w}) \in dom(\mathbb{M})) (Inv \land p) \Rightarrow (Inv \land p') \circ c \qquad (Inv \land p) \Rightarrow (g' \circ c) \Rightarrow g (Inv, \Delta, \Psi); (p', g', \mathbb{A}, \mathbb{G}) \vdash \mathbb{I} \qquad (Inv, \Delta, \Psi); (p, g, \mathbb{A}, \mathbb{G}) \vdash c; \mathbb{I}$$

(ST)

Rules for conditional branching instructions are similar to the JD rule, which are straightforward to understand.

$$\begin{array}{l} (\mathbf{p}',\mathbf{g}',\mathbb{A}',\mathbb{G}') = \Psi(\mathbf{f}) & \mathbb{A} \Rightarrow \mathbb{A}' & \mathbb{G}' \Rightarrow \mathbb{G} \\ \forall \mathbb{S}.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) > \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{p}' \ \mathbb{S}) \\ \forall \mathbb{S}.\mathcal{M}'.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) > \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{g}' \ \mathbb{S} \ \mathbb{M}') \Rightarrow (\mathbf{g} \ \mathbb{S} \ \mathbb{M}') \\ \forall \mathbb{S}.\mathcal{M}'.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) \leq \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{p}'' \ \mathbb{S}) \\ \forall \mathbb{S}.\mathcal{M}'.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) \leq \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{g}'' \ \mathbb{S} \ \mathbb{M}') \Rightarrow (\mathbf{g} \ \mathbb{S} \ \mathbb{M}') \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}'', \mathfrak{g}'', \mathbb{A}, \mathbb{G}) \vdash \mathbb{I} \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}, \mathbf{g}, \mathbb{A}, \mathbb{G}) \vdash \mathsf{bgt} \ \mathbf{r}_s, \mathbf{r}_t, \mathbf{f}; \mathbb{I} \\ \end{array}$$

(BGT)

$\begin{array}{l} (\mathbf{p}',\mathbf{g}',\mathbb{A}',\mathbb{G}') = \Psi(\mathbf{f}) & \mathbb{A} \Rightarrow \mathbb{A}' & \mathbb{G}' \Rightarrow \mathbb{G} \\ \forall \mathbb{S}.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) = \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{p}' \ \mathbb{S}) \\ \forall \mathbb{S}.\forall \mathbb{M}'.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) = \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{g}' \ \mathbb{S} \ \mathbb{M}') \Rightarrow (\mathbf{g} \ \mathbb{S} \ \mathbb{M}') \\ \forall \mathbb{S}.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) \neq \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{p}'' \ \mathbb{S}) \\ \forall \mathbb{S}.\forall \mathbb{M}'.(\mathit{Inv} \land \mathbf{p}) \ \mathbb{S} \Rightarrow (\mathbb{S}(\mathbf{r}_s) \neq \mathbb{S}(\mathbf{r}_t)) \Rightarrow (\mathbf{g}'' \ \mathbb{S} \ \mathbb{M}') \Rightarrow (\mathbf{g} \ \mathbb{S} \ \mathbb{M}') \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}'', \mathbf{A}, \mathbb{G}) \vdash \mathbb{I} \\ \hline (\mathit{Inv}, \Delta, \Psi); (\mathbf{p}, \mathbf{g}, \mathbb{A}, \mathbb{G}) \vdash \mathsf{beq} \ \mathbf{r}_s, \mathbf{r}_t, \mathbf{f}; \mathbb{I} \end{array}$

#### 4.5 Soundness of CMAP

The soundness of CMAP inference rules with respect to the operational semantics of the machine is established following the syntactic approach of proving type soundness [39]. From the "progress" and "preservation" lemmas, we can guarantee that given a wellformed program under compatible assumptions and guarantees, the current instruction sequence will be able to execute without getting "stuck". Furthermore, any safety property derivable from the global invariant will hold throughout the execution. We define  $\mathbb{P} \stackrel{n}{\longmapsto} \mathbb{P}'$  as the relation of *n*-step  $(n \ge 0)$  program transitions. The soundness of CMAP is formally stated as Theorem 4.3.

#### Lemma 4.1 (Progress)

$\Phi = (Inv, \Delta, \Psi). If there exist \Theta, p, g, A and G such that$  $<math display="block">\Phi; \Theta; (p, g, A, G) \vdash ((\mathbb{M}, \mathbb{R}), \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I}), then (Inv \mathbb{M}), and there$  $exists a program \widetilde{\mathbb{P}} such that ((\mathbb{M}, \mathbb{R}), \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I}) \longmapsto \widetilde{\mathbb{P}}.$

# Lemma 4.2 (Preservation)

If  $\Phi; \Theta; (p, g, \mathbb{A}, \mathbb{G}) \vdash \mathbb{P}$  and  $\mathbb{P} \longmapsto \widetilde{\mathbb{P}}$ , where  $\mathbb{P} = (\mathbb{S}, \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I})$ and  $\widetilde{\mathbb{P}} = (\widetilde{\mathbb{S}}, \widetilde{\mathbb{Q}}, \mathbb{T}, \mathbb{C}, \widetilde{\mathbb{I}})$ , then there exist  $\widetilde{\Theta}, \widetilde{p}, \widetilde{g}, \widetilde{\mathbb{A}}$  and  $\widetilde{\mathbb{G}}$  such that  $\Phi; \widetilde{\Theta}; (\widetilde{p}, \widetilde{g}, \widetilde{\mathbb{A}}, \widetilde{\mathbb{G}}) \vdash \widetilde{\mathbb{P}}$ .

#### Theorem 4.3 (Soundness)

$\Phi = (Inv, \Delta, \Psi). If there exist \Theta, p, g, A and G such that$  $<math display="block">\Phi; \Theta; (p, g, A, G) \vdash \mathbb{P}_0, then for any n \ge 0, there exist M, \mathbb{R},$  $Q, \mathbb{T}, \mathbb{C} and \mathbb{I} such that \mathbb{P}_0 \stackrel{n}{\longmapsto} ((\mathbb{M}, \mathbb{R}), \mathbb{Q}, \mathbb{T}, \mathbb{C}, \mathbb{I}) and (Inv \mathbb{M}).$

The proofs for these two lemmas and the soundness theorem are given in Appendix A. We have also implemented the complete CMAP system [10] in the Coq proof assistant so we are confident that CMAP is indeed sound and can be used to certify general multi-threaded programs.

# 5. Examples

## 5.1 Unbounded Dynamic Thread Creation

In Figure 3 we showed a small program main2 which spawns child threads within a while loop. This kind of unbounded dynamic thread creation cannot be supported using the cobegin/coend structure. We show how such a program is specified and verified using our logic. To simplify the specification, we trivialize the function f and g and let f(i) = i and  $g(x, _) = x + 1$ .

We assume the high-level program works in a preemptive mode. Figure 10 shows the CMAP implementation, where yield instructions are inserted to simulate the preemption. This also illustrates that our logic is general enough to simulate preemptive thread model.

To verify the safety property of the program, the programmer need find a global invariant and specifications for each static thread and the code heap. In Figure 10 we show definitions of assertions that are used to specify the program. Proof sketches are also inserted in the program. For ease of reading, we use named variables as short-hands for their values in memory. The primed variables represent the value of the variable after state transition. We also introduce the shorthand [r] for  $\mathbb{R}(r)$ .

The following formulae show the specifications of static threads, and the initial memory and instruction sequence.

$\begin{array}{l} \mathit{Inv} \equiv \mathtt{True} \\ \Delta \ \equiv \{\mathtt{main} \rightsquigarrow (\mathtt{True}, \mathbb{A}_0, \mathbb{G}_0), \mathtt{chld} \rightsquigarrow (\mathtt{p}, \mathbb{A}, \mathbb{G})\} \\ \Psi \ \equiv \{\mathtt{loop} \rightsquigarrow (\mathtt{p}', \mathbb{G}_1, \mathbb{A}_1, \mathbb{G}_1), \mathtt{cont} \rightsquigarrow (\mathtt{p}_3, \mathbb{G}_3, \mathbb{A}_3, \mathbb{G}_3)\} \\ \mathtt{Initial} \ \mathbb{M} \equiv \{\mathtt{data} \rightsquigarrow \_, \dots, \mathtt{data} + 99 \rightsquigarrow \_\} \\ \mathtt{Initial} \ \mathbb{I} \ \equiv \mathtt{movi} \ \mathtt{r}_0, 0; \ \mathtt{movi} \ \mathtt{r}_1, 1; \ \mathtt{movi} \ \mathtt{r}_2, 100; \ \mathtt{jd} \ \mathtt{loop} \end{array}$